Device model is the key of an excellent SPICE simulator. TJSPICE provides robust device model support ranging from classical device models to new advanced ones. Benefiting from state of the art device model implementation algorithms, TJSPICE shows golden accuracy compared to current industry golden SPICE tool while with higher efficiency. Device models ranging from the Compact Modeling Council (CMC) standardized models (BSIM, PSP, HiSIM, etc.) on the latest technology nodes to models designed for specified applications have been proven.

For SI/PI applications, TJSPICE provides sound support of S parameter, transmission line/VIA, and latest version (IBIS 7.0) of IBIS/IBIS-AMI model. By this TJSPICE can be used in chip/package/PCB SI/PI analysis in pre-layout stage and in post-layout sign-off stage as a golden spice simulator.

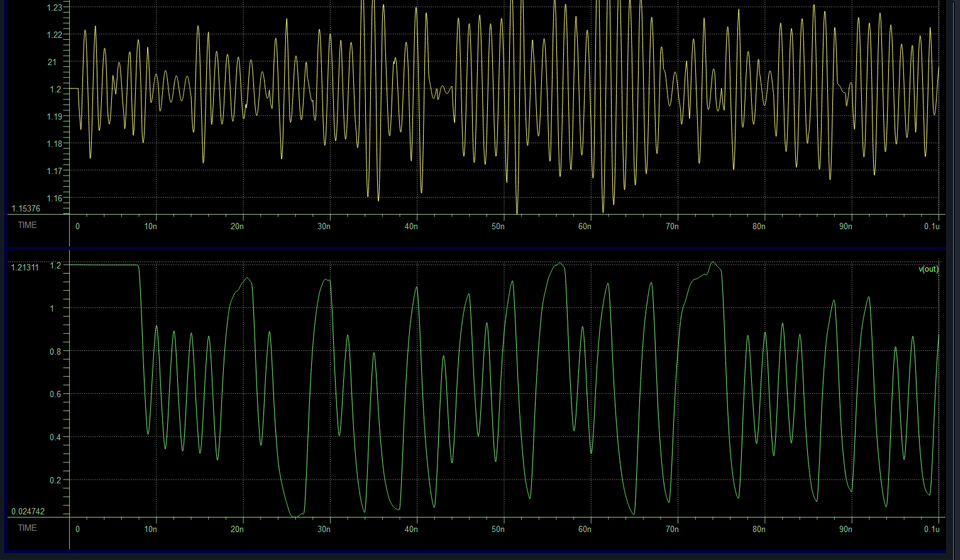

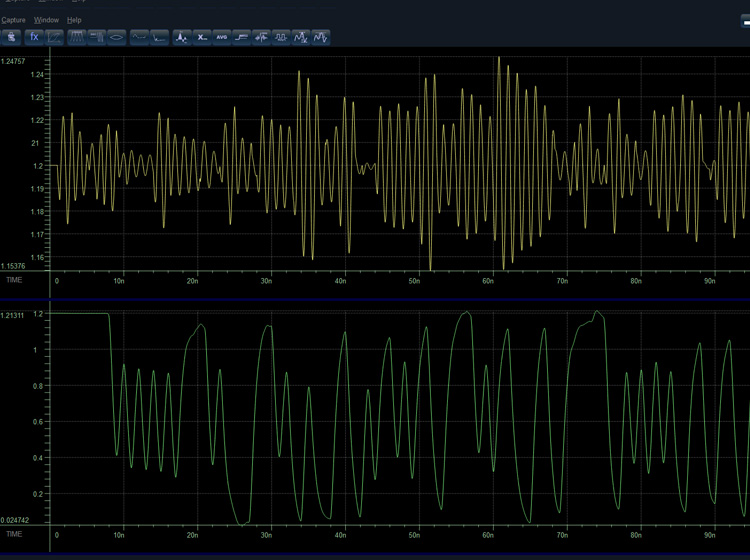

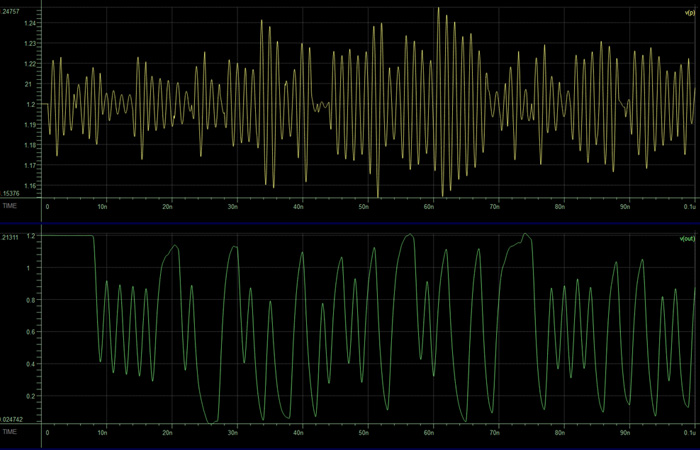

Transient, linear, and statistical analyses are available in TJSPICE for users to do all kinds of what-if analysis and design check in different application fields. All simulation results can be displayed and post-processed by Julin’s waveform viewing tool.

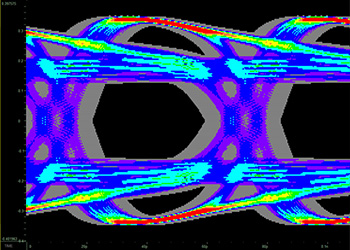

TJSPICE’s statistical analysis allows designers to do both traditional single-ended IO (DDR, etc.) SI analysis and SERDES differential SI analysis. Statistical analysis is especially important in BER estimation for SERDES interfaces which needs billions of bits simulation. This is beyond traditional true-spice simulation’s limit.

R、L、C、G、E、F、G、H

S parameter/wide-band spice model

Transmission line, via

IBIS、IBIS-AMI

MOSFET/BJT/diode (All commonly used versions)

Commonly used voltage/current sources (. vec, .vcd included)

DC Analysis

AC Analysis

Transient Analysis

Statistical eye-diagram analysis

PDA(Peak Distortion Analysis)

Bit by bit Transient Analysis

Related Download