Product Details

Julin SIDesigner is an Electronic Design Automation (EDA) platform for modern high-speed digital systems.

Leveraging its core Golden-accuracy SPICE engine, it provides precise, one-stop SI/PI analysis and timing sign-off for integrated systems spanning the chip, package, and board levels.

Key Highlights

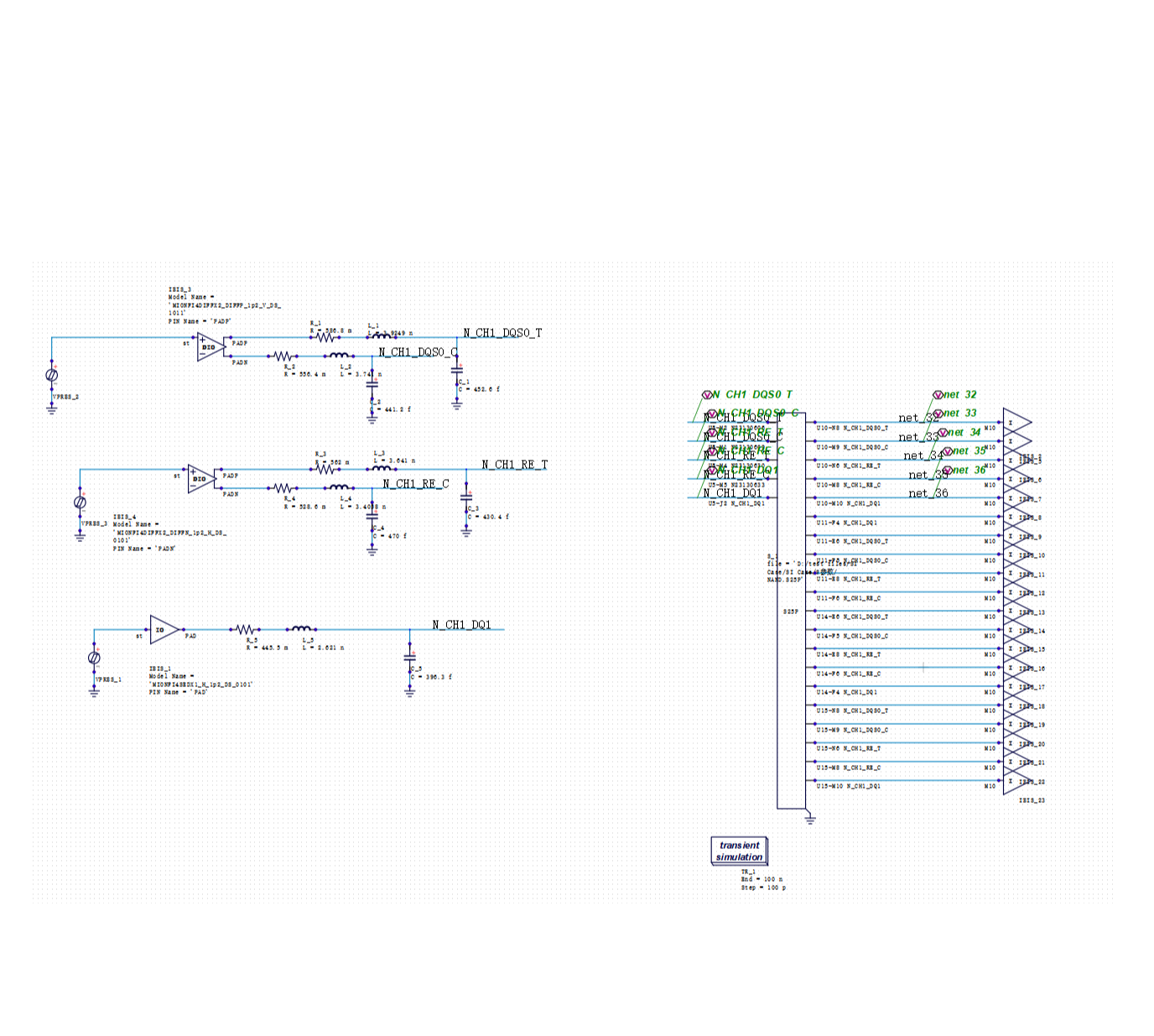

Full-Link System Coordination (Co-Simulation)

· Integrates chip-package-board interconnect effects to achieve closed-loop validation of signal, power, and timing at the system level.

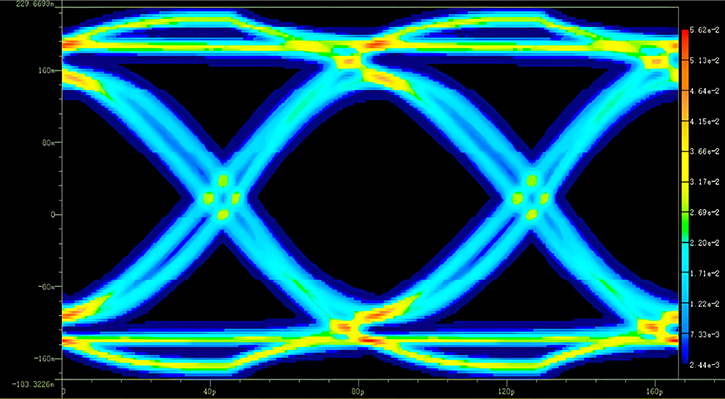

Sign-off Grade Simulation Accuracy

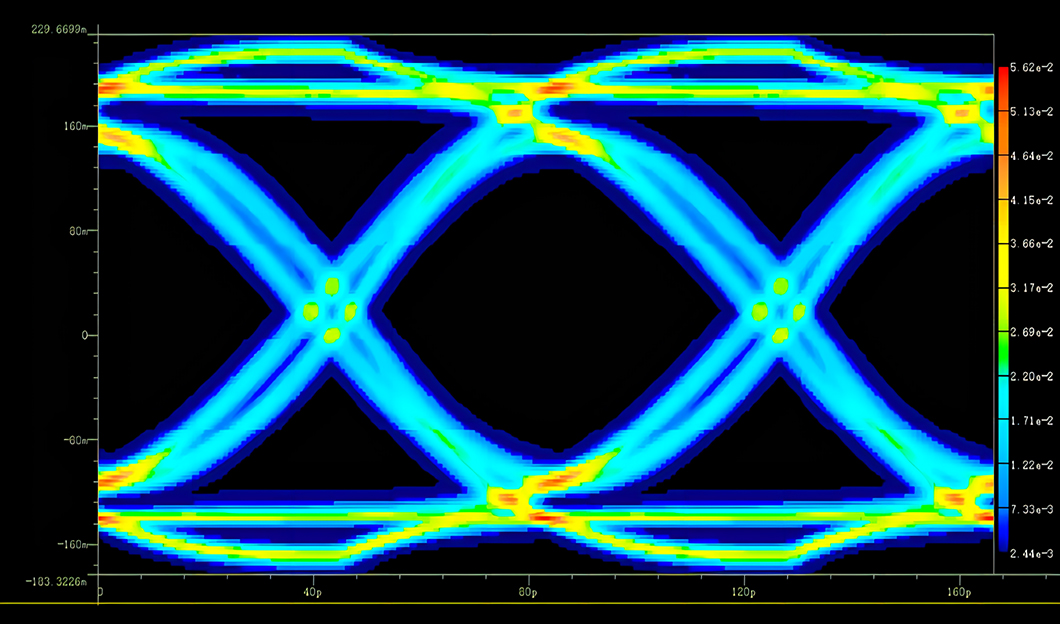

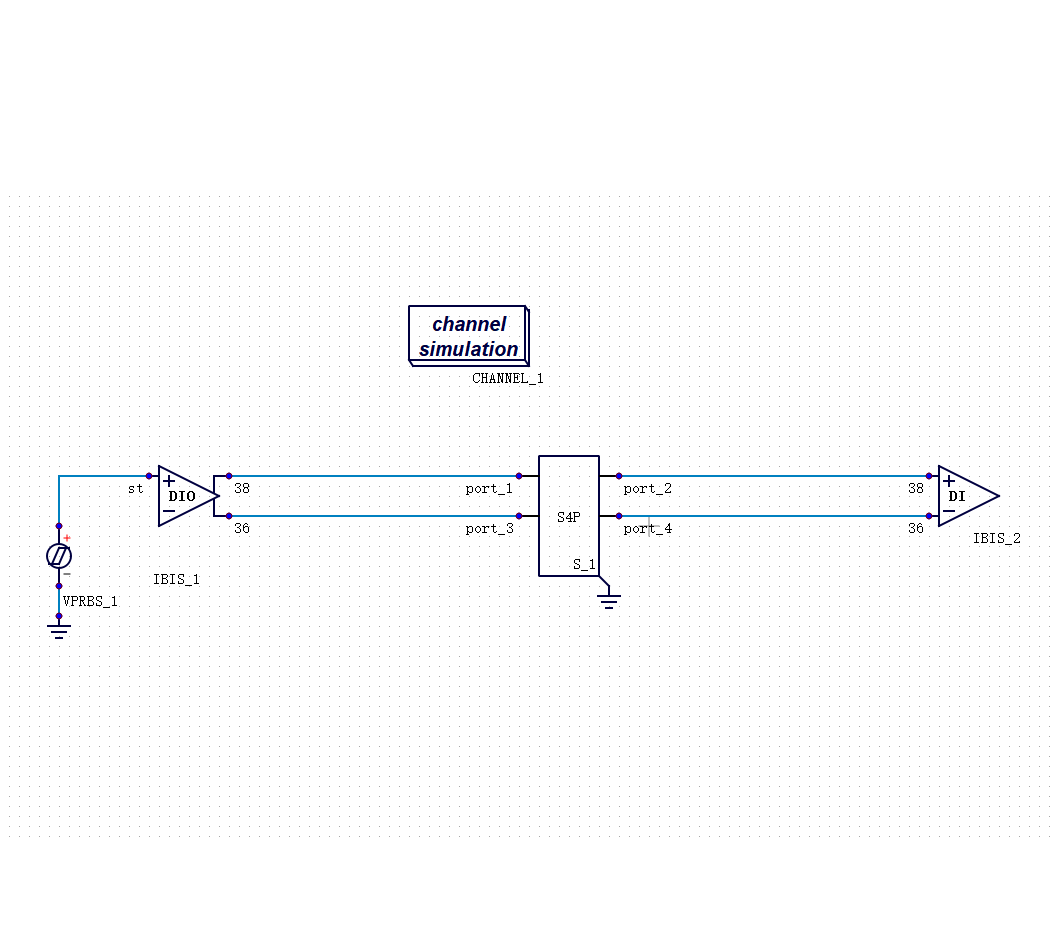

· The built-in TJSPICE Golden-accuracy simulation engine achieves industry-recognized sign-off standards in both True-SPICE time-domain simulation and Channel simulation, demonstrating outstanding convergence and stability.

Pre-Layout Exploration and Optimization

· Supports rapid "what-if" analysis of topology, termination, and power networks during the pre-layout stage, mitigating SI/PI risks at the source and minimizing iterative cycles.

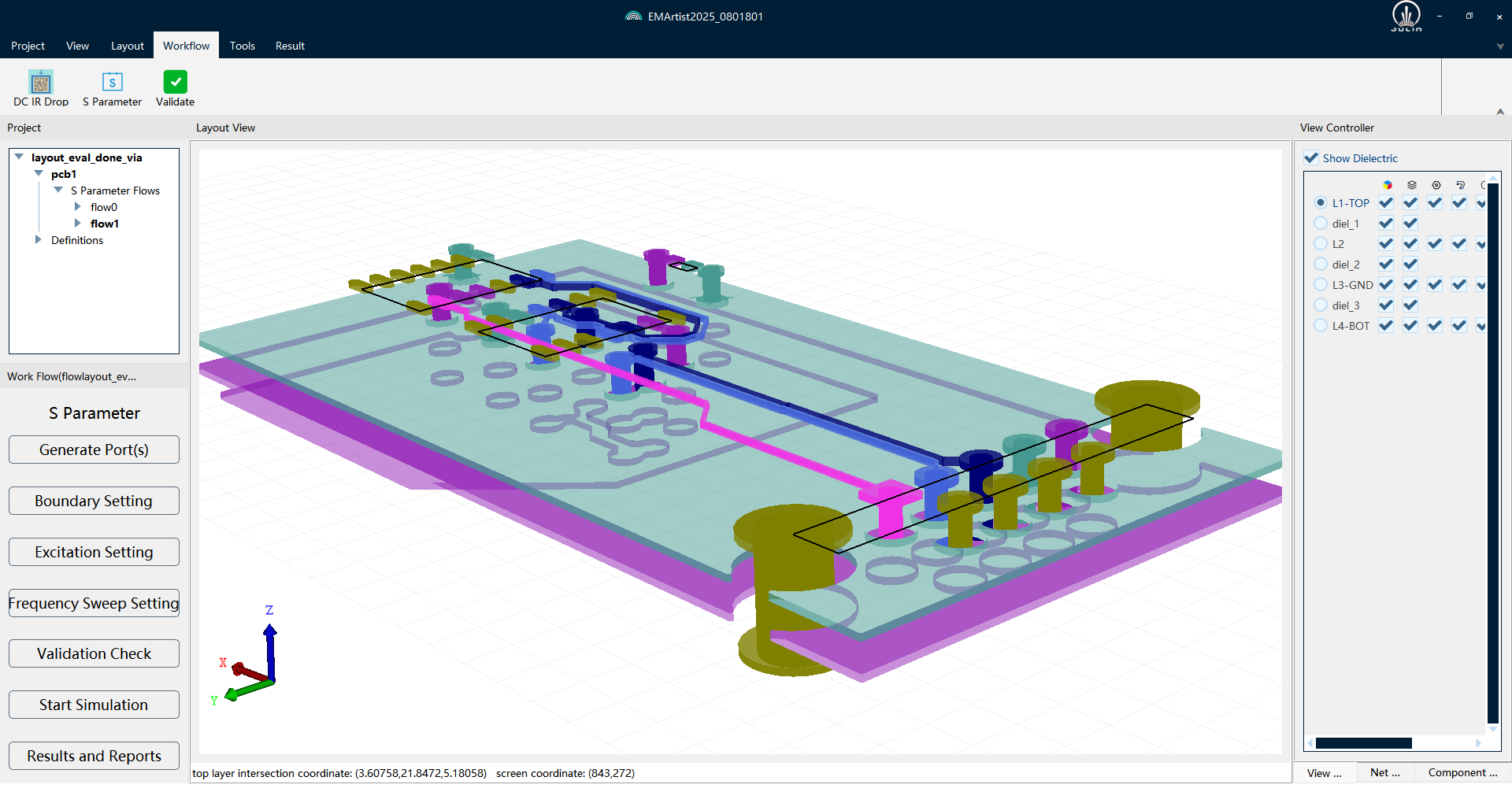

Heterogeneous Modeling and Co-Simulation

· Integrates with third-party 3D Full-Wave Solvers to enable circuit-electromagnetic co-simulation, allowing for the precise handling of complex interconnects and package structures.

Comprehensive High-Speed Interface Validation

· Provides dedicated simulation workflows for parallel interfaces (e.g., DDR/HBM/UCIE) and SerDes interfaces (e.g., PCIe/MPI/USB/XSR), meeting the high-bandwidth requirements of 5G/AI and similar scenarios.

Unified Platform and Workflow Integration

· Completes the entire workflow—from AC analysis and transient simulation to system-level parameter validation—within a single environment. It supports customization and integration with other design tools, boosting efficiency and data consistency.

Advantages and Value Proposition

-

Sign-off Grade Accuracy

SIDesigner's simulation accuracy is highly consistent with industry Golden Standard tools, with errors generally below 1%. This performance is particularly outstanding in the simulation of complex parallel buses like DDR and HBM. This provides engineers with a reliable basis for sign-off, ensuring first-pass design success.

-

Comprehensiveness: Full-Link High-Speed Interface Coverage from Chip to Board

The platform has been validated for comprehensive support of both parallel interfaces (e.g., DDR/HBM) and high-speed SerDes interfaces (e.g., PCIe/XSR). This demonstrates the capability to address the design and validation needs of mainstream and cutting-edge interfaces in the 5G/AI era.

-

Powerful Core: Unified Simulation Engine Balancing Efficiency and Accuracy

Within a single platform, SIDesigner seamlessly integrates Transient Simulation (for accurate time-domain waveforms in DDR/HBM), Statistical Simulation (for fast channel analysis in PCIe), and Bit-by-Bit Analysis (for complex modulated signals like XSR PAM4). This provides users with the optimal solution for various stages of the design process.

-

Core Value: Enabling Precise Decisions and Accelerating Time-to-Market

By providing trustworthy simulation data, SIDesigner helps engineers accurately predict system performance and optimize design bottlenecks early in the design phase. This leads to a substantial reduction in expensive hardware iterations, significantly shortening the R&D cycle, and lowering development costs and risks.

Product Features

-

Simulation and Analysis Capabilities

Time-Domain Analysis: Offers Golden-level accuracy for Transient analysis, as well as Bit-by-Bit and Statistical analysis, accurately assessing signal waveforms and timing.

Frequency-Domain Analysis: Supports AC analysis for evaluating system frequency response characteristics and power impedance.

Channel Analysis: Integrates passive channel validation to quickly diagnose interconnect link performance.

DFQ Analysis: Built-in Monte Carlo and Yield analysis functions to assess system robustness under process variations.

Other Simulation Functions: Supports system-level Power Integrity (PI) transient noise analysis, signal net Time-Domain Reflectometry (TDR) analysis, and Peak Distortion Analysis (PDA), providing a one-stop package for all necessary circuit-level SI/PI simulation functionalities.

-

Model and Library Support

Basic Component Library: Provides a complete library of passive device models (R, L, C, E, F, G, H, etc.).

Interconnect Modeling: Natively supports transmission line, via, and S-parameter models, accurately characterizing 3D electromagnetic effects.

Active and Behavioral Models: Fully compatible with Wide-Band SPICE models, IBIS/IBIS-AMI models, and transistor-level IO models.

Open Integration: Supports user-defined sub-circuit import and allows flexible configuration of various signal sources.

-

Design Workflow and Automation

Efficient Schematic Design: Supports intuitive component placement, hierarchical design, and intelligent wiring features.

Dedicated Design Flows: Provides a complete simulation flow for DDR interfaces and modeling wizards for transmission lines/vias.

Automated Design and Optimization: Integrates Design of Experiments (DOE) and Peak Distortion Analysis (PDA) tools to enable automatic exploration and optimization of critical design parameters.

-

Platform and Usability

Intuitive Interactive Interface: Adopts an easy-to-master graphical user interface (GUI), reducing the learning curve.

Powerful Result Visualization: Built-in high-performance waveform viewer supports quick viewing and precise measurement of simulation results.

Comprehensive Technical Support: Comes equipped with detailed help documentation and learning resources, ensuring users receive timely technical assistance.

Related Scenarios

-

UFS 3/4

UFS 3/4UFS 3/4 mainly addresses flash memory storage used in digital cameras, smart phones and other consumer electronics. While providing high data transfer speed and stability, it also reduces consumer confusion about the various memory card formats on the market and the use of different memory card adapters

-

eMMC

eMMCeMMC is mainly used in embedded storage media such as smart phones and tablet computers and other consumer smart mobile devices

-

HDMI

HDMIHDMI is mainly used for high quality audio and video transmission

-

DPHY

DPHYDPHY Mainly used in applications including connecting cameras, audio, storage, RF and providing chip-to-chip inter-processor (IPC) communication

-

LPDDR 3/4/5

LPDDR 3/4/5LPDDR 3/4/5 is mainly used in mobile devices and embedded systems that need to be used for a long time, such as cell phones and tablet PCs

-

MPHY

MPHYMPHY Main applications include connecting cameras, audio, storage, RF and providing chip-to-chip inter-processor (IPC) communications

-

MIPI

MIPIMIPI is mainly used in mobile device interface

-

CXL

CXLCXL is mainly used to solve the problem of large memory

-

CPHY

CPHYCPHY is mainly used in mobile devices with high transmission rates

-

DDR 3/4/5

DDR 3/4/5DDR 3/4/5 Mainly used in areas such as computers, servers and other high performance computing devices

-

NAND

NANDNAND is mainly used in high-capacity data storage, such as smartphones, PCs, tablets, USB flash drives, SSDs, servers, etc

-

PCIe 4/5/6

PCIe 4/5/6PCIe 4/5/6 Mainly graphics cards, network cards, storage devices, etc. Through the PCIe interface, high-speed communication can be carried out between the devices, thus improving the efficiency and speed of data transmission

Related Industries

-

Communication Industry

With the advent of the 5G+ era, high-speed transmission will provide strong support for improving the communication rate between chips and upgrading the network rate. The transmission of ultra-high-speed signals on communication chips is particularly important to the simulation of signal integrity, and JULIN tools help customers in the industry to improve design efficiency and control the quality of verification.

-

Memory Industry

DDR3/4/5, LPDDR3/4/5 protocol read/write rate steps up, the industry standard high-speed memory has a broad market prospect, high-precision ultra-high-speed read/write signal simulation is crucial. Julin tools help customers in the industry to improve design efficiency and control verification quality.

-

Big Data Center GPU Industry

With the advent of the information age, massive data fills people's daily life. Data center provides functions including storage, data management, data processing and transmission, and is an important entity for large-scale high-performance computing and massive data storage, providing strong support for the construction of information technology, and the data center's important performance indexes such as large capacity, large bandwidth, large arithmetic power, low latency, high energy efficiency, and high reliability require that information transmission and Processing should be completed with extremely fast speed and high precision quality, which requires more accurate, high-speed simulation focusing on signal integrity.

-

IOT Industry

The Internet of Things (IoT) connects various “things” in the physical world with the Internet, collects data through smart devices, sensors, etc., and then processes, and stores the information through the network to realize smart management and control, and in the era of 5G+, the IoT will rely on the scale effect of mobile networks to support the future of the hundreds of billions of IoT. Behind the ultra-high-speed signals and large bandwidth is the need for more accurate signal integrity simulation.

-

Product

Details -

Featured

Advantages -

Product

Value -

Related

Scenarios -

Related

Industries