产品简介

以签核级精度覆盖从芯片、封装到板级的一站式系统 SI/PI 仿真平台

巨霖SIDesigner是面向现代高速数字系统的电子设计自动化平台,通过其核心的Golden精度SPICE引擎,为从芯片、封装到电路板的集成系统提供精准的一站式SI/PI分析与时序签核。

核心能力:

· 全链路系统协同

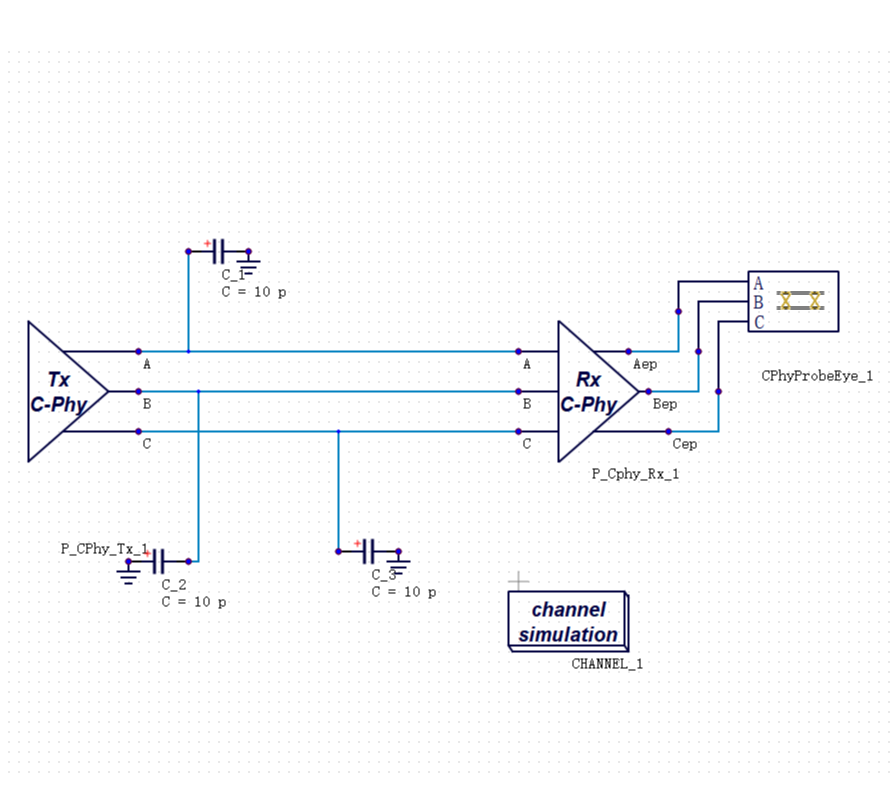

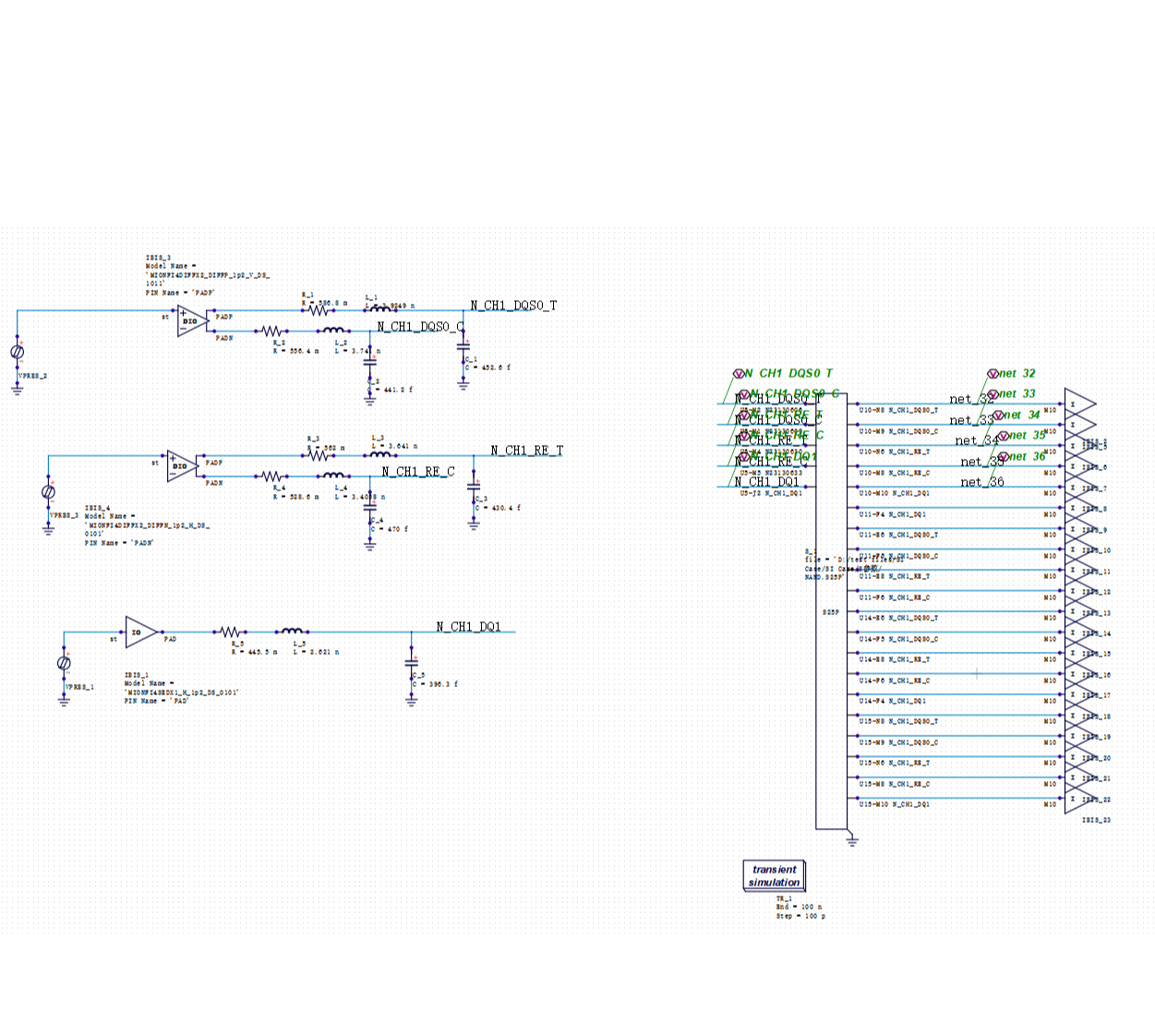

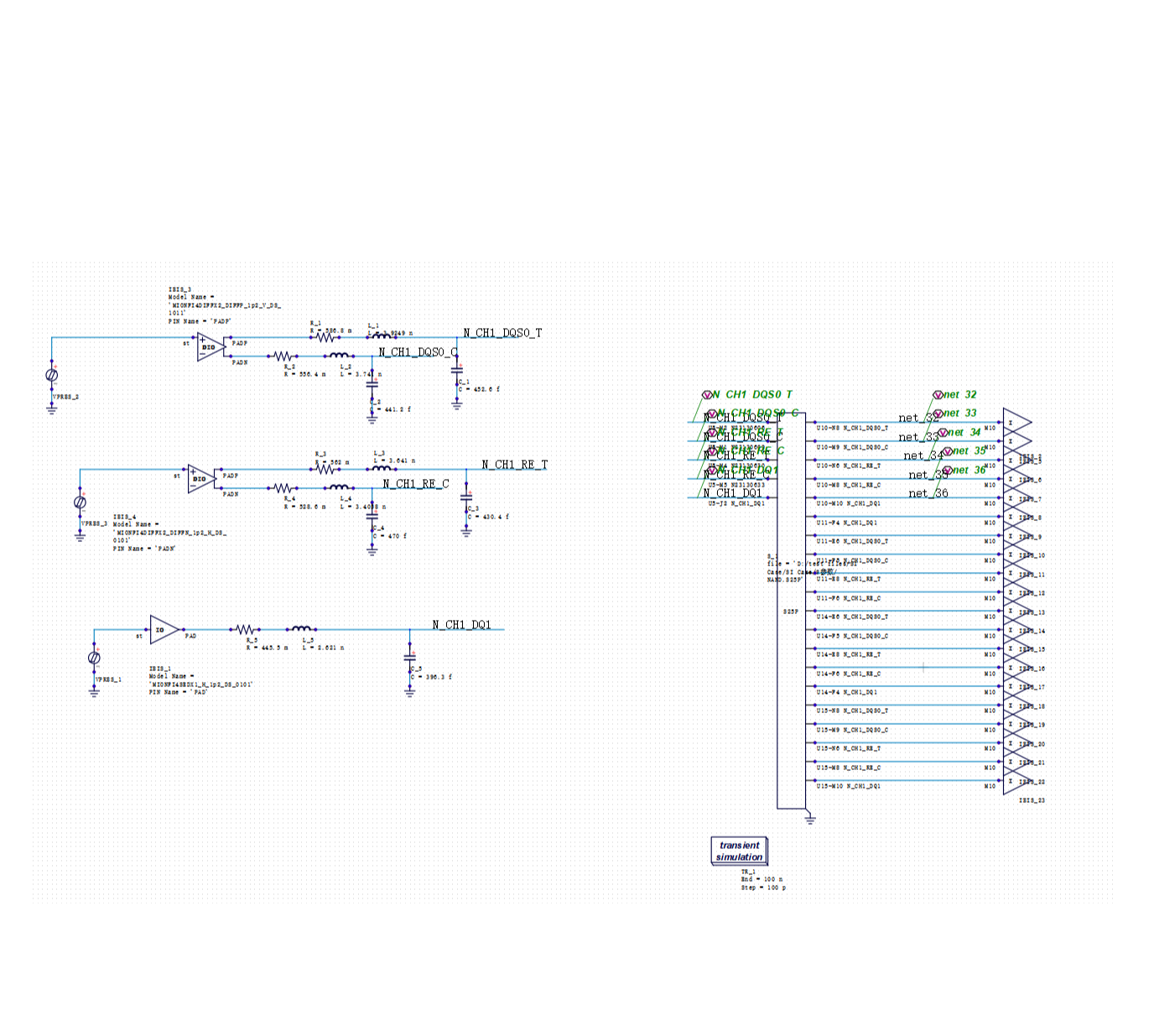

整合芯片-封装-板级互连效应,在系统层面完成信号、电源与时序的闭环验证。

· 签核级仿真精度

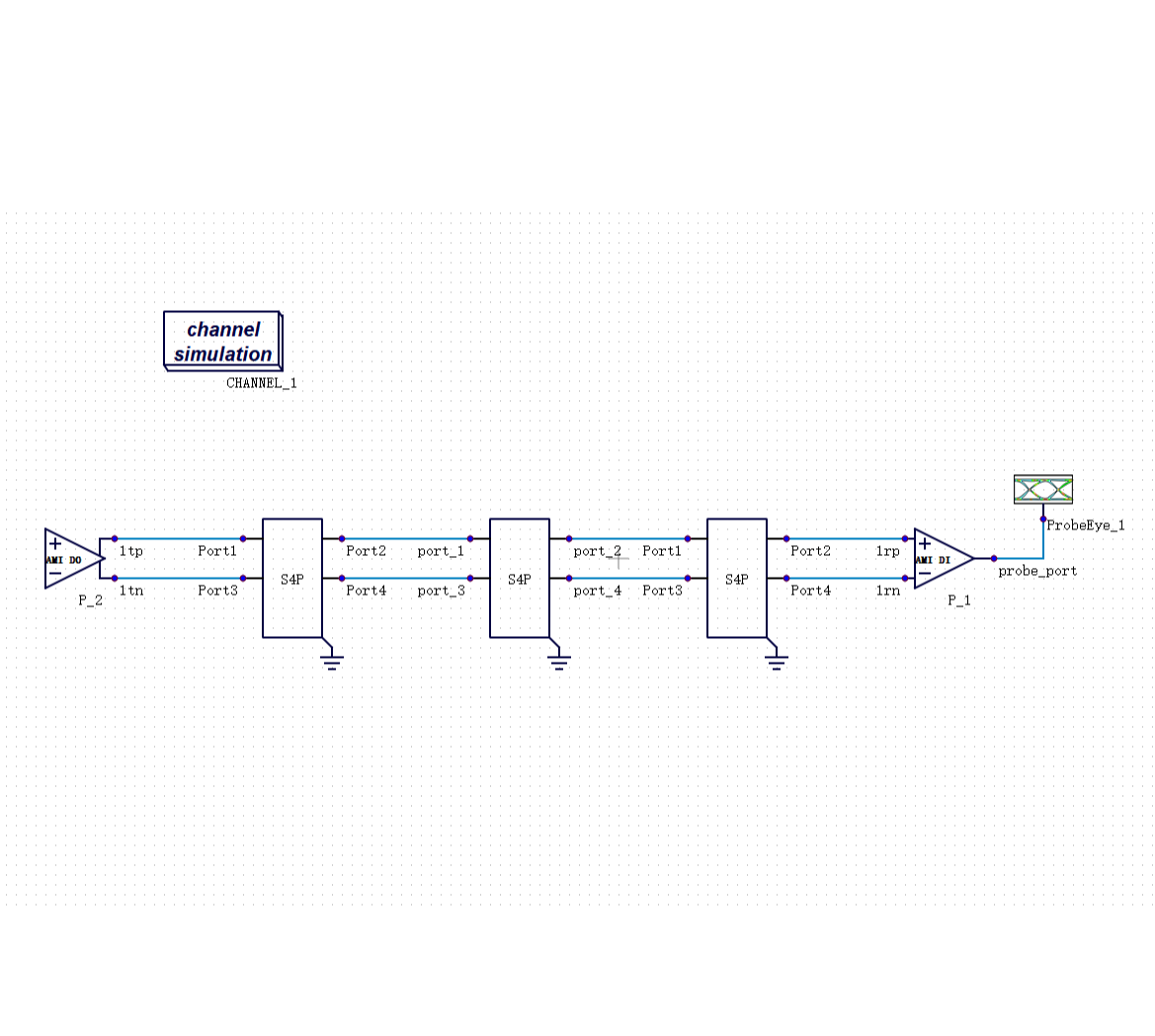

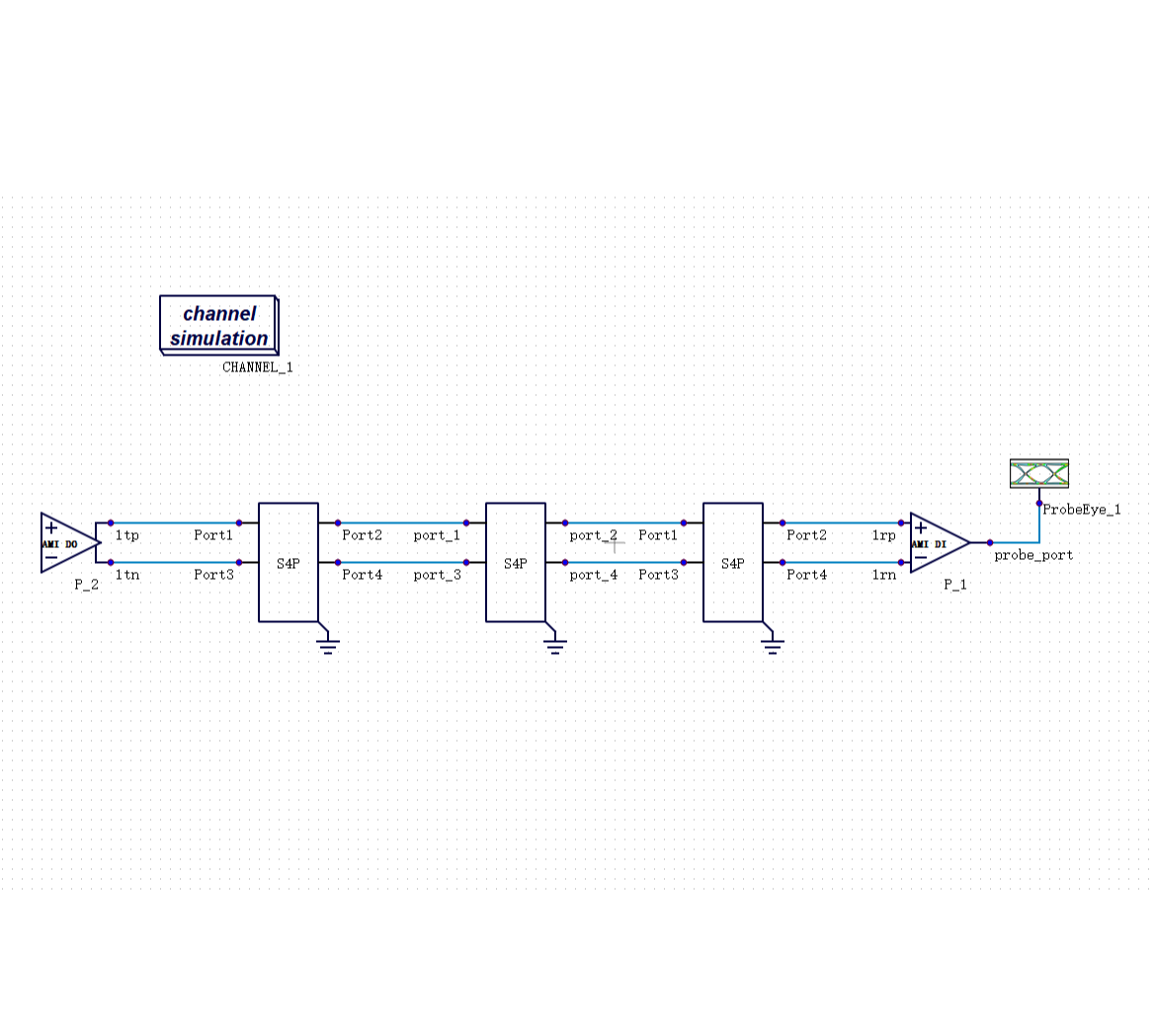

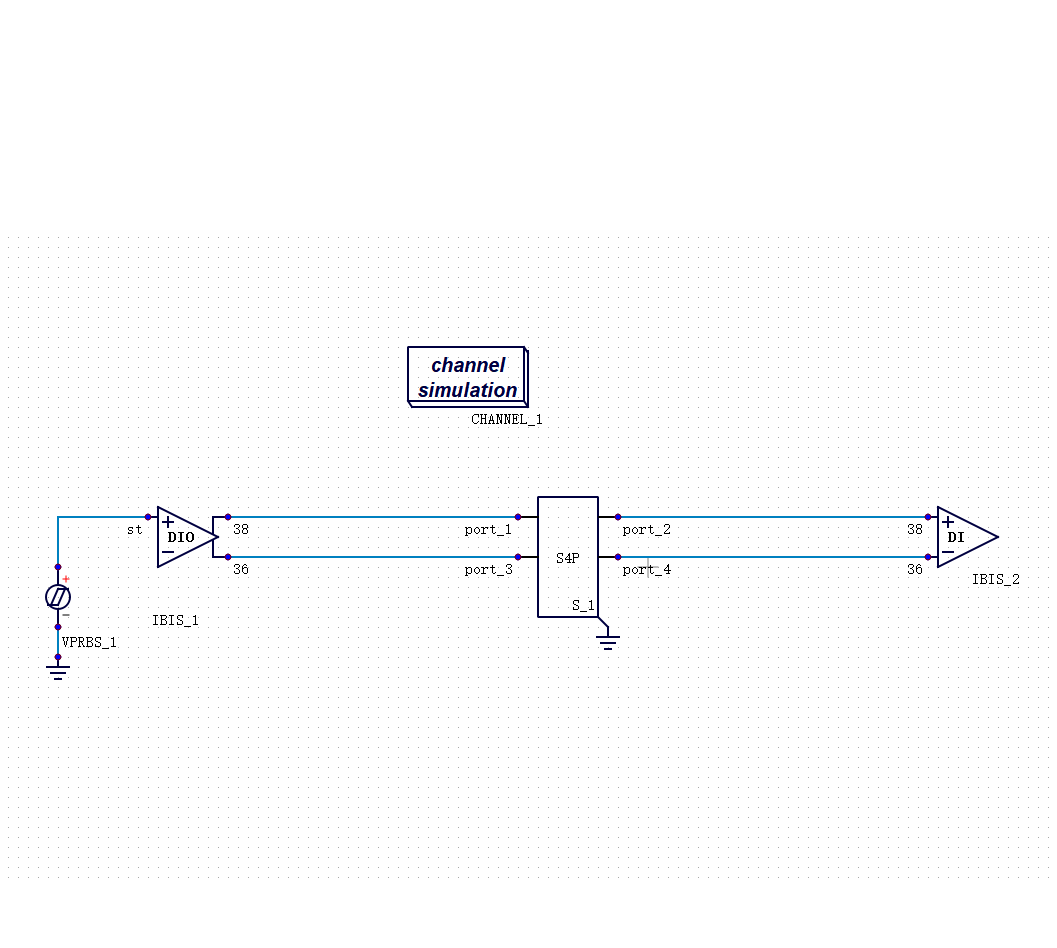

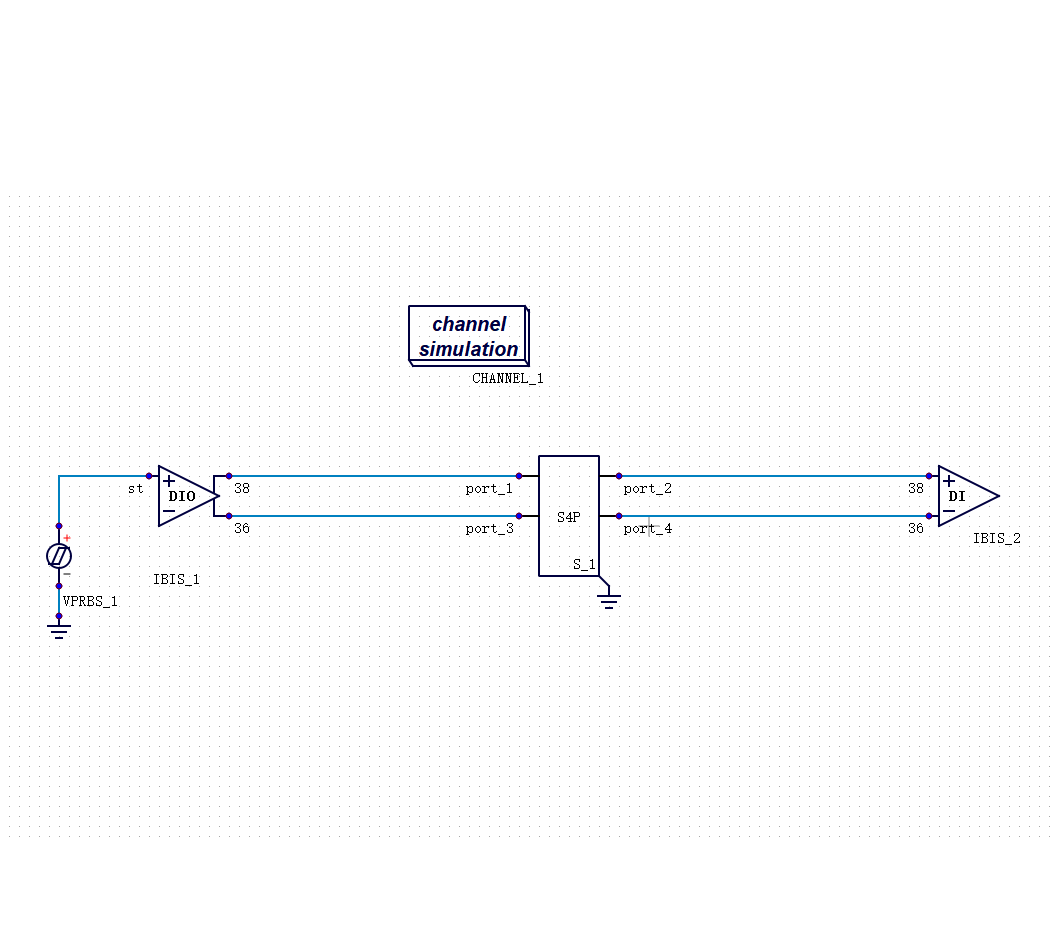

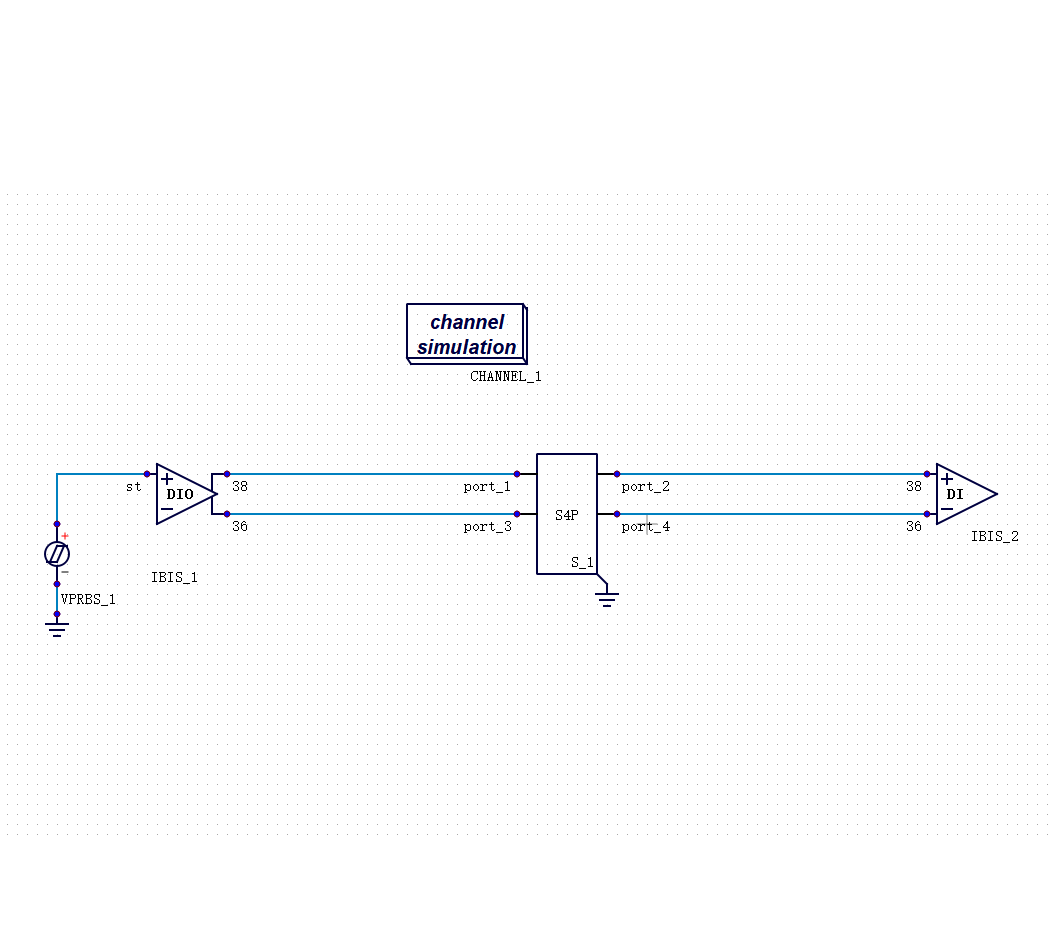

内置TJSPICE Golden精度仿真引擎,在True-SPICE时域仿真与Channel信道仿真中实现业界公认的签核标准,收敛性与稳定性表现卓越。

· 预布局探索与优化

支持在布局前期进行拓扑、端接与电源网络的快速假设分析,从源头规避SI/PI风险,减少反复迭代。

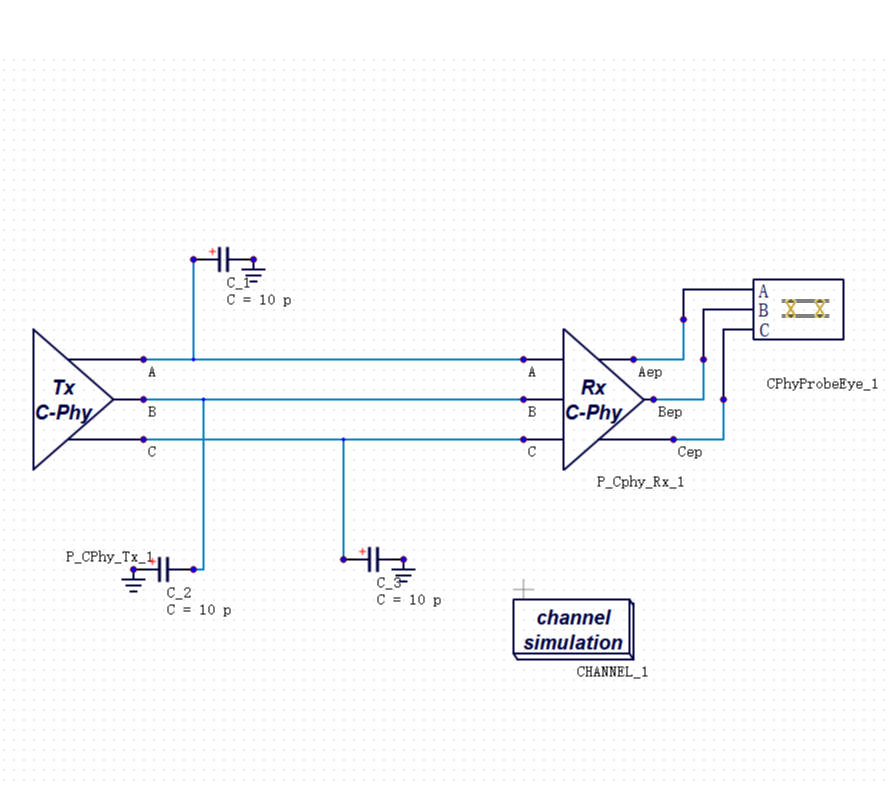

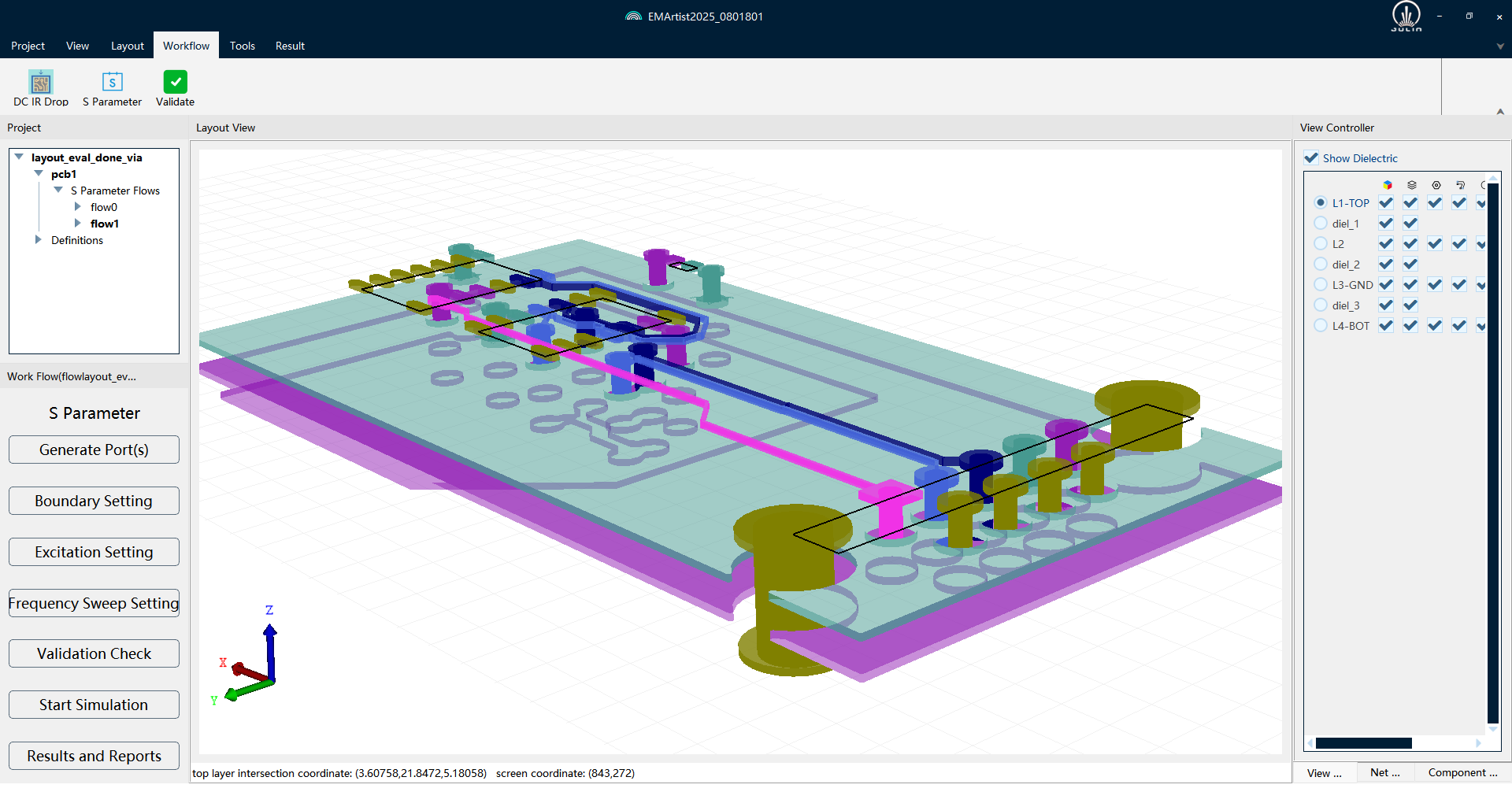

· 异构建模与协同仿真

借助第三方3D全波求解器,可实现电路-电磁协同仿真,精准处理复杂互联与封装结构。

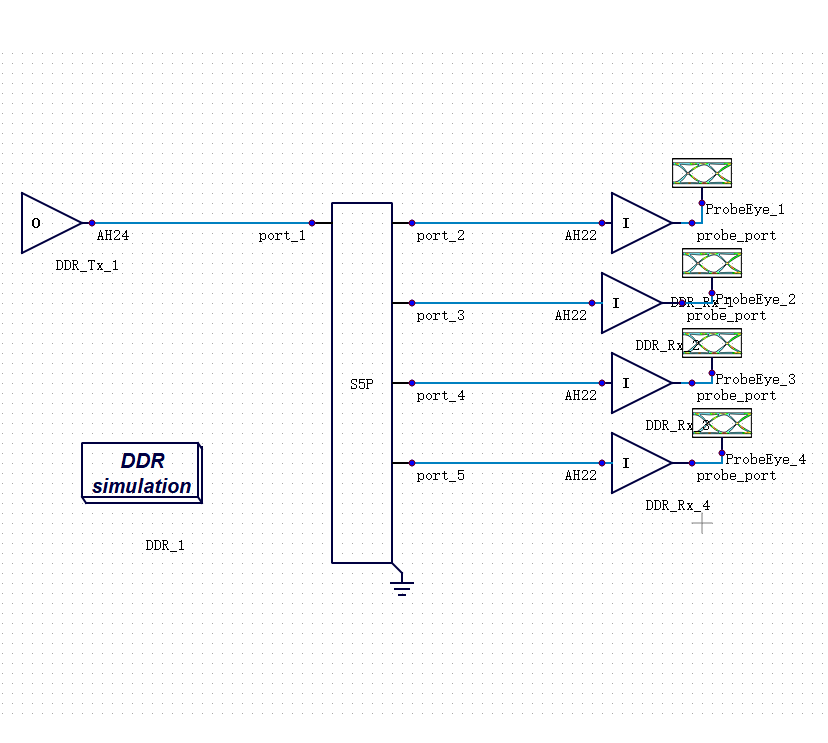

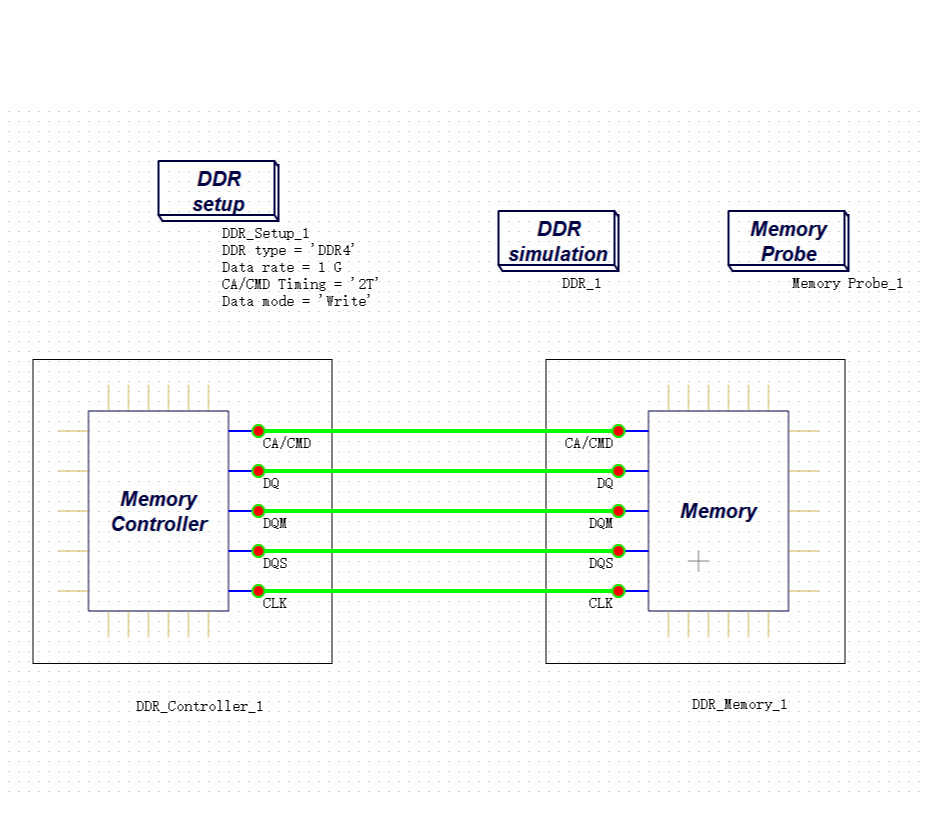

· 高速接口完整验证

提供DDR/HBM/UCIE等并行接口与PCIe/MPI/USB/XSR等SerDes接口的专用仿真流程,满足5G/AI等高带宽场景要求。

· 统一平台与流程集成

在单一环境中完成从AC分析、瞬态仿真到系统级参数验证的全流程,支持脚本定制与设计工具集成,提升效率与数据一致性。

优势与价值

-

签核级精度

SIDesigner的仿真精度与行业Golden标准工具高度一致,误差普遍低于1%,在DDR、HBM等复杂并行总线仿真中表现尤为卓越。这为工程师提供了可靠的签核依据,确保设计一次成功。

-

全面性:覆盖从芯片到板级的全链路高速接口

平台已验证对DDR/HBM(并行接口)与PCIe/XSR(高速SerDes)的全面支持,具备应对5G/AI时代主流及前沿接口的设计与验证能力。

-

强大内核:统一的仿真引擎,兼顾效率与精度

SIDesigner在同一平台内,无缝集成了瞬态仿真(用于DDR/HBM的精确时域波形)、统计仿真(用于PCIe的快速通道分析)与Bit-by-Bit分析(用于XSR PAM4的复杂调制信号),为用户在不同设计阶段提供最优解决方案。

-

核心价值:赋能精准决策,加速产品上市

通过提供可信赖的仿真数据,SIDesigner帮助工程师在设计前期精准预测系统性能、优化设计瓶颈,从而大幅减少硬件迭代次数,显著缩短研发周期,降低开发成本与风险。

产品功能

-

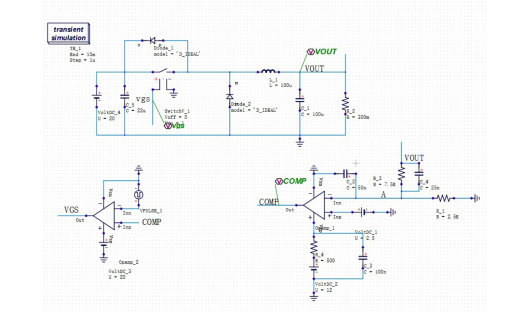

仿真分析能力

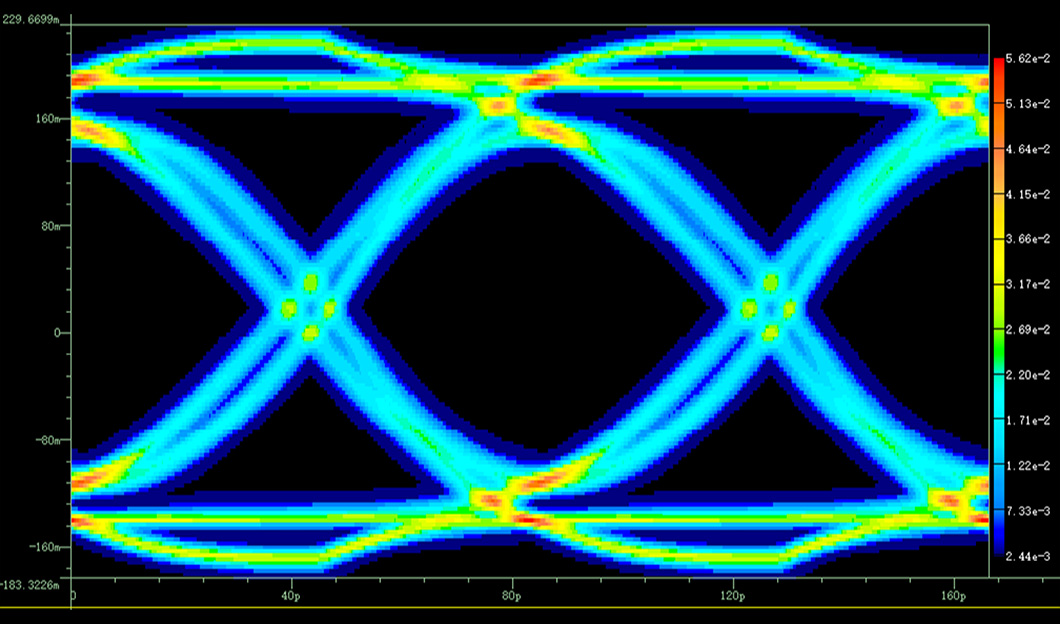

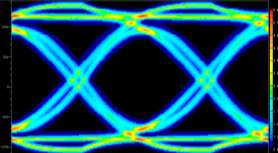

时域分析:提供Golden级别精度的瞬态分析及Bit-by-Bit与统计分析,精确评估信号波形与时序。

频域分析:支持AC分析,用于评估系统频响特性与电源阻抗。

通道分析:集成无源通道验证,快速诊断互连链路性能。

DFQ分析:内建蒙特卡洛与良率分析功能,评估系统在工艺偏差下的鲁棒性。

其它仿真功能:支持系统级电源完整性瞬态噪声分析、信号网络TDR分析以及峰值失真分析(PDA)等,一站式打包SI/PI电路级仿真可能用到的所有功能。

-

模型与库支持

基础元件库:提供完整的R、L、C、E、F、G、H等无源器件模型。

互连建模:原生支持传输线、过孔及S参数模型,精确表征三维电磁效应。

有源与行为级模型:全面兼容宽带SPICE模型、IBIS/IBIS-AMI模型及晶体管级IO模型。

开放集成:支持用户自定义子电路导入,并可灵活配置各类信号源。

-

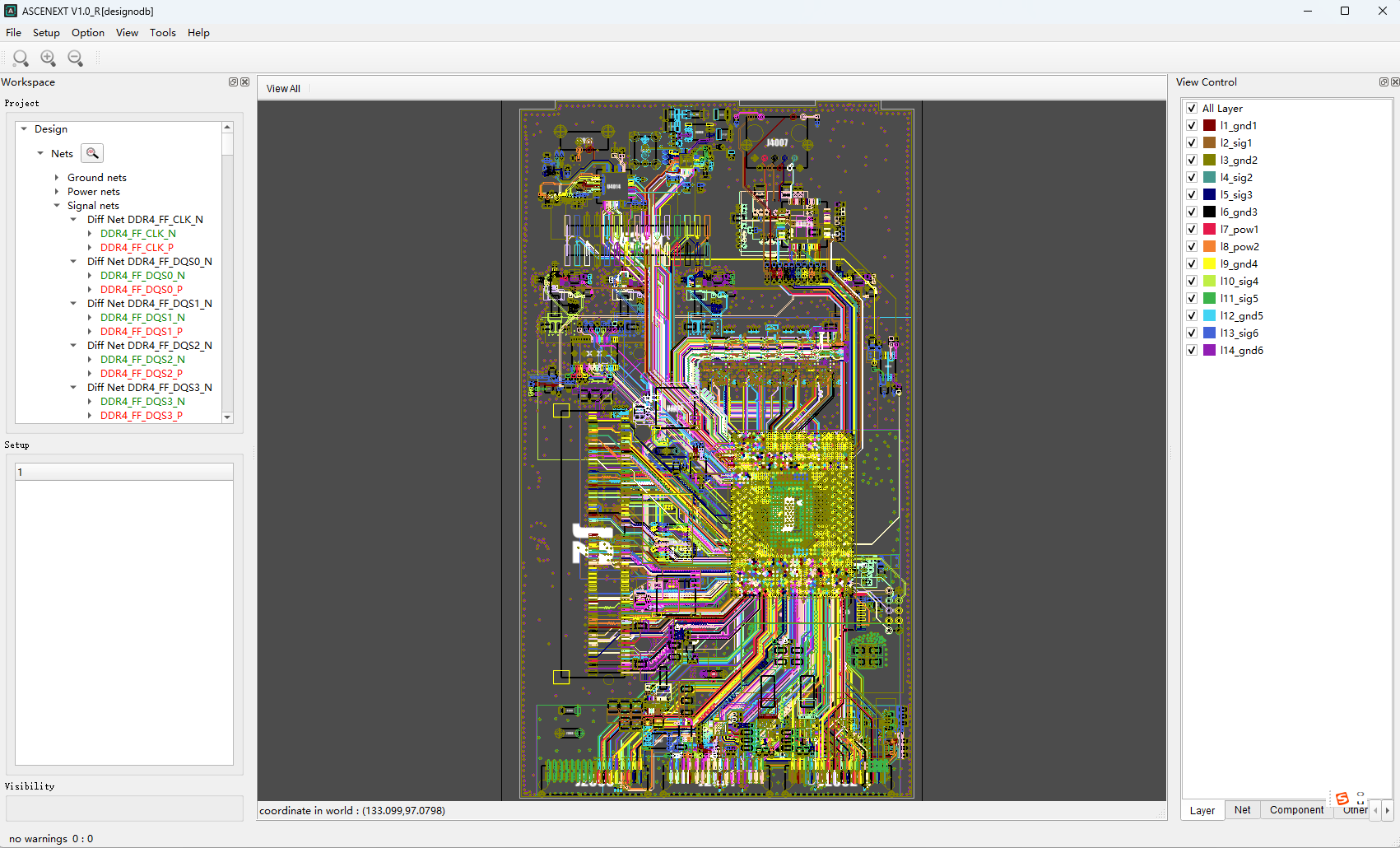

设计流程与自动化

高效原理图设计:支持直观的元器件摆放、层次化设计及智能连线功能。

专用设计流程:提供针对DDR接口的完整仿真流程与传输线/过孔建模向导。

自动化设计与优化:集成实验设计(DOE)与峰值失真分析(PDA)工具,实现关键设计参数的自动探索与优化。

-

平台与可用性

直观的交互界面:采用易于掌握的图形化界面,降低学习曲线。

强大的结果可视化:内置高性能波形显示器,支持仿真结果的快速查看与精准测量。

全面的技术支持:配备详尽的帮助文档与学习资源,确保用户可获得及时的技术支持。

-

产品详情

-

特点优势

-

产品价值