产品详情

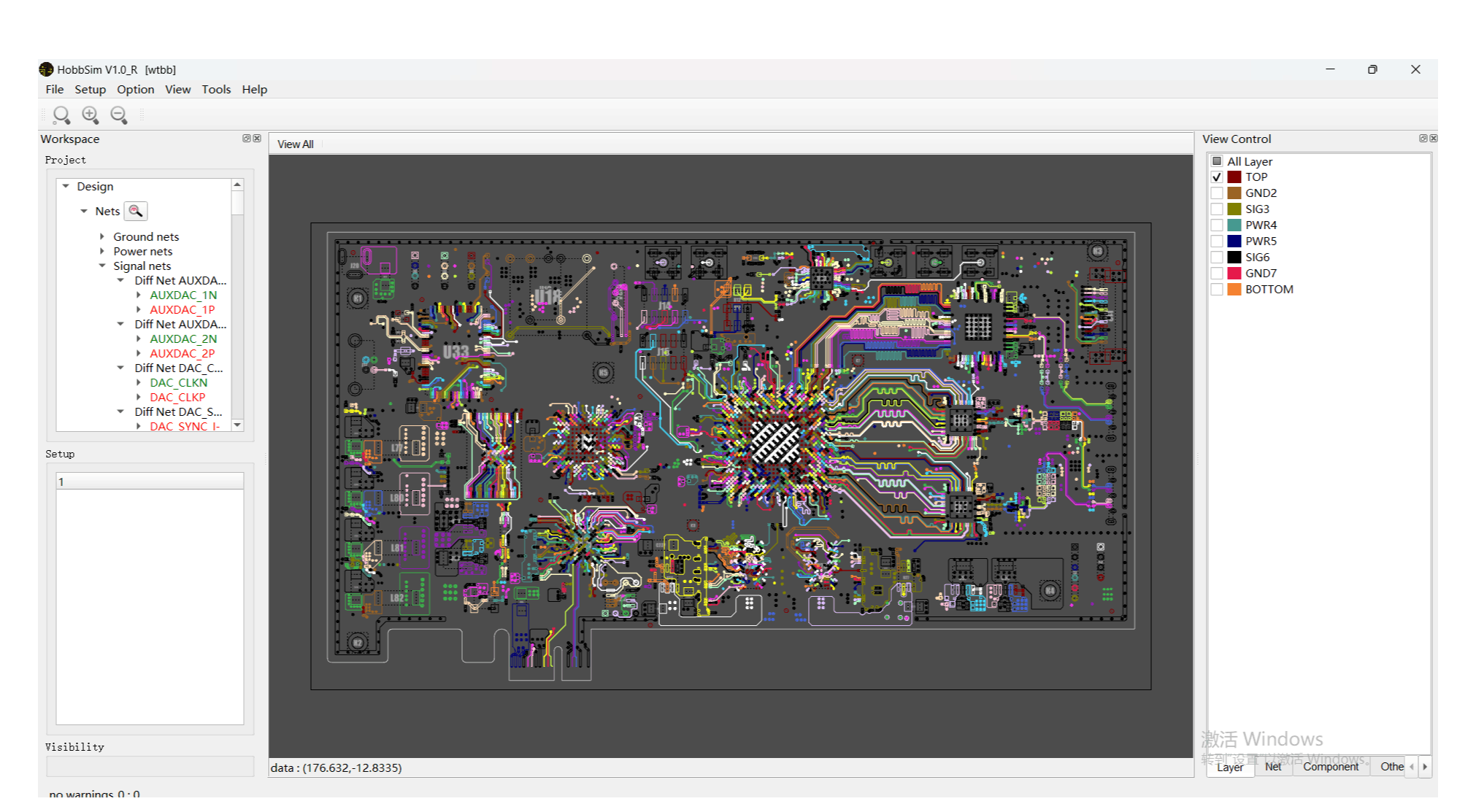

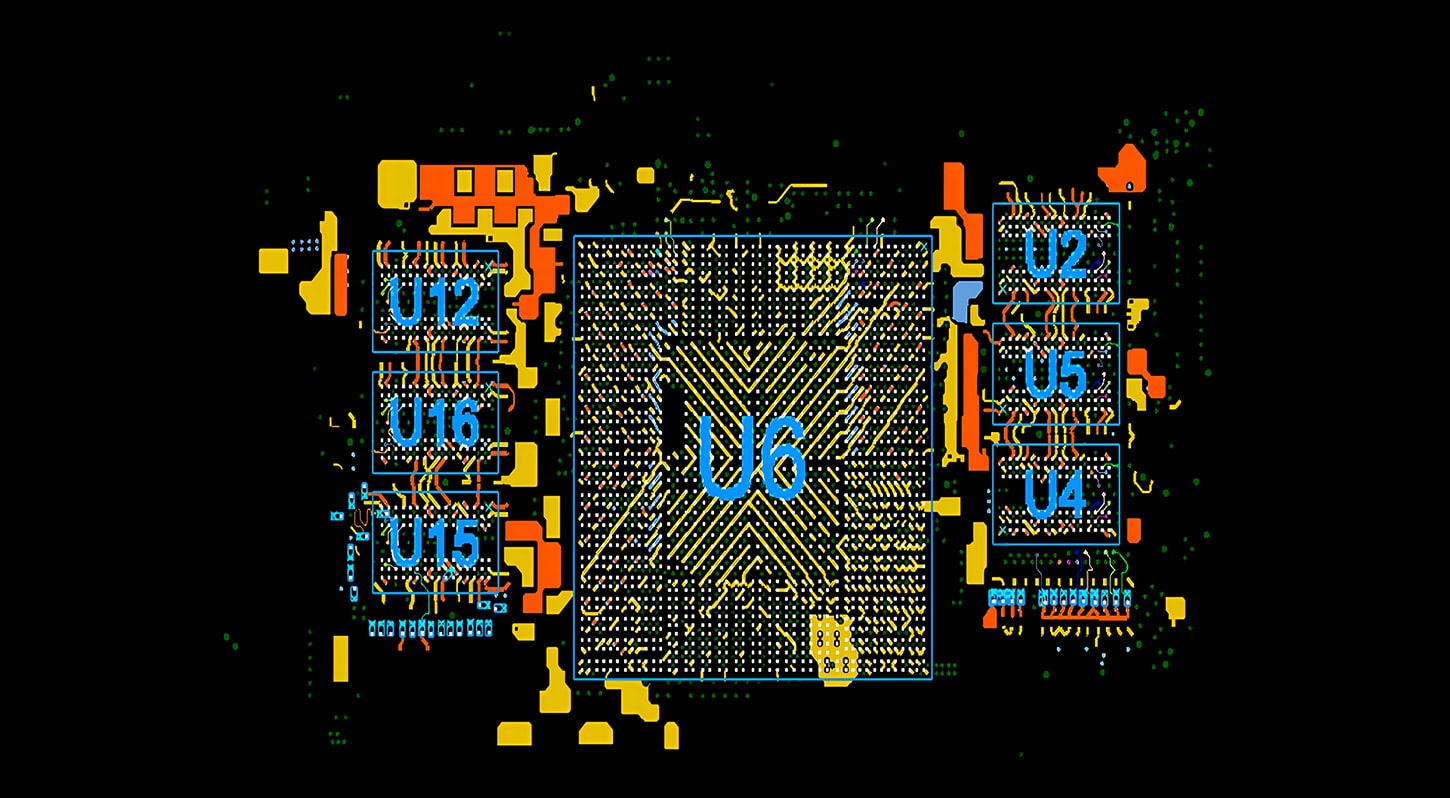

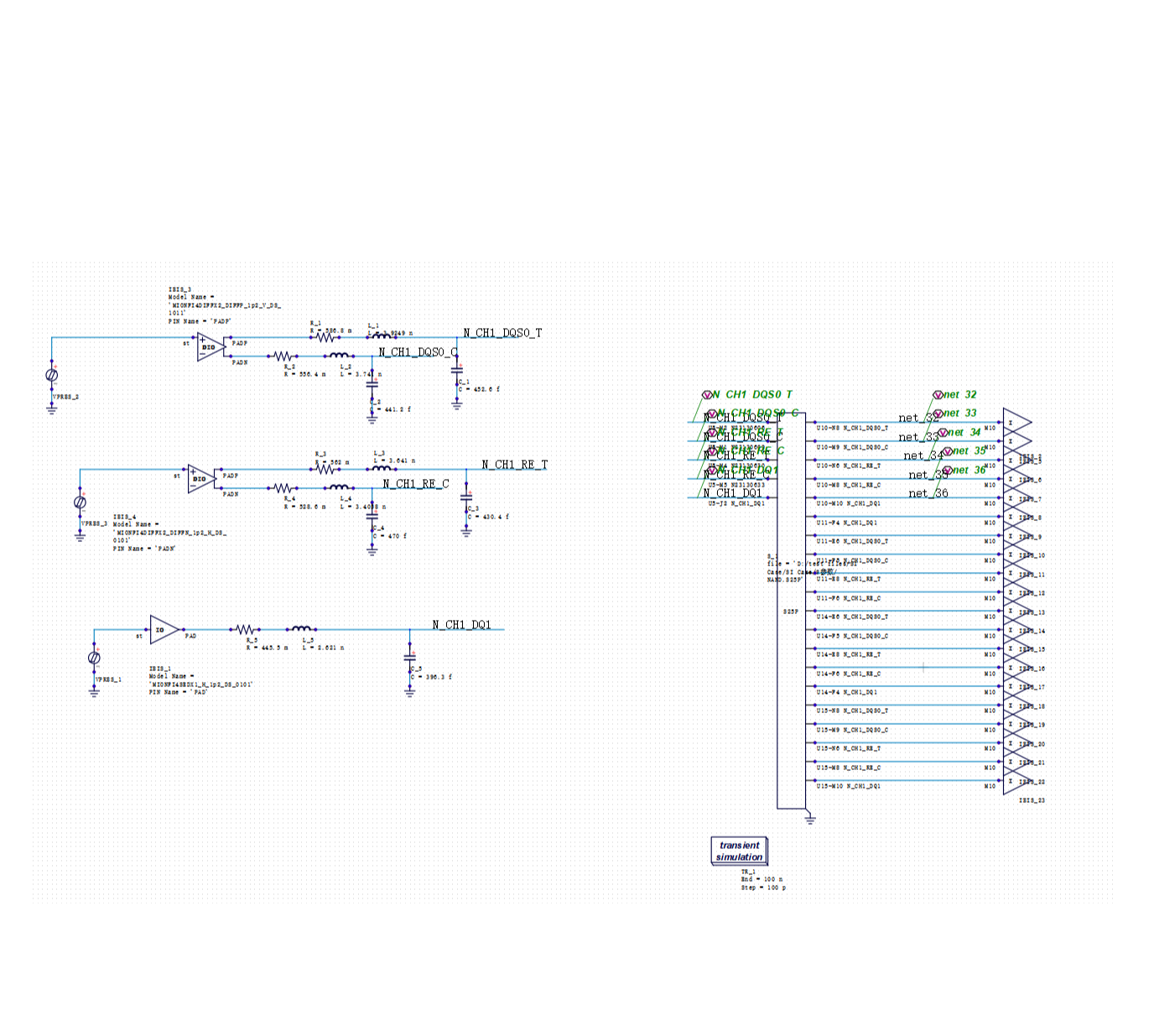

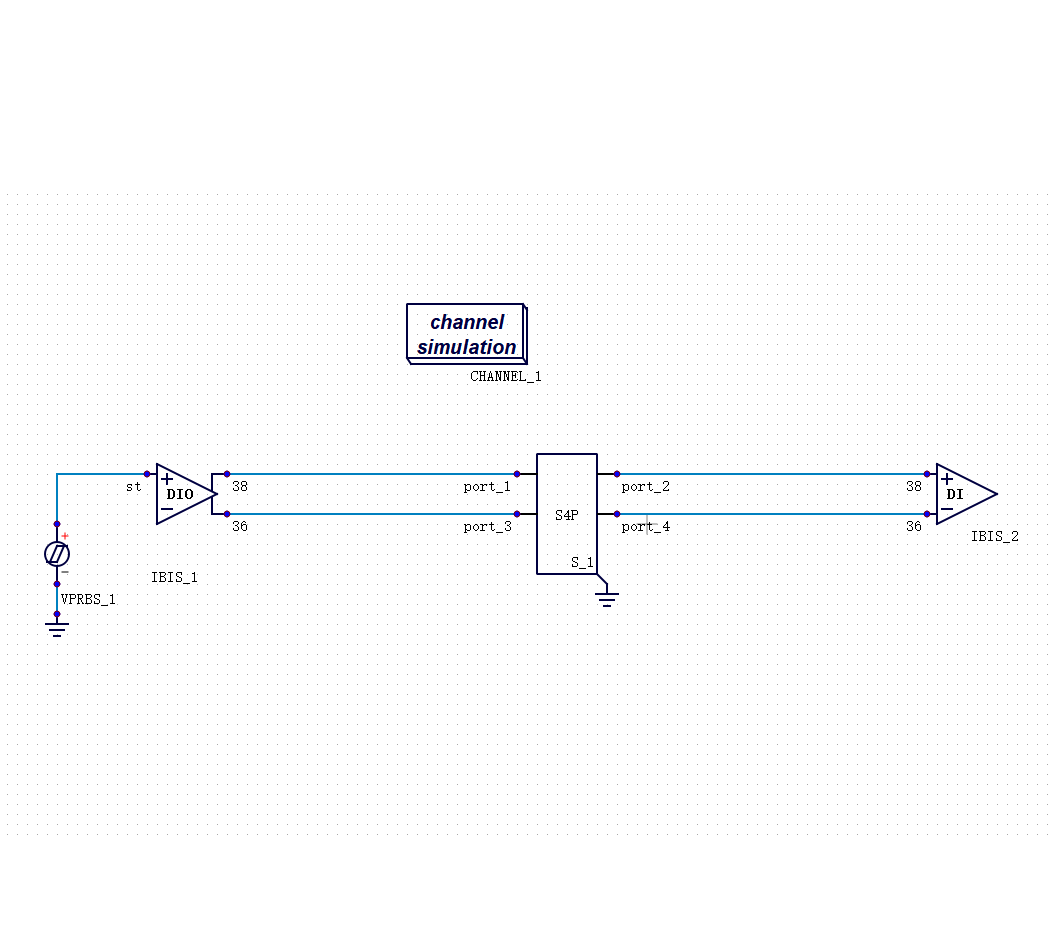

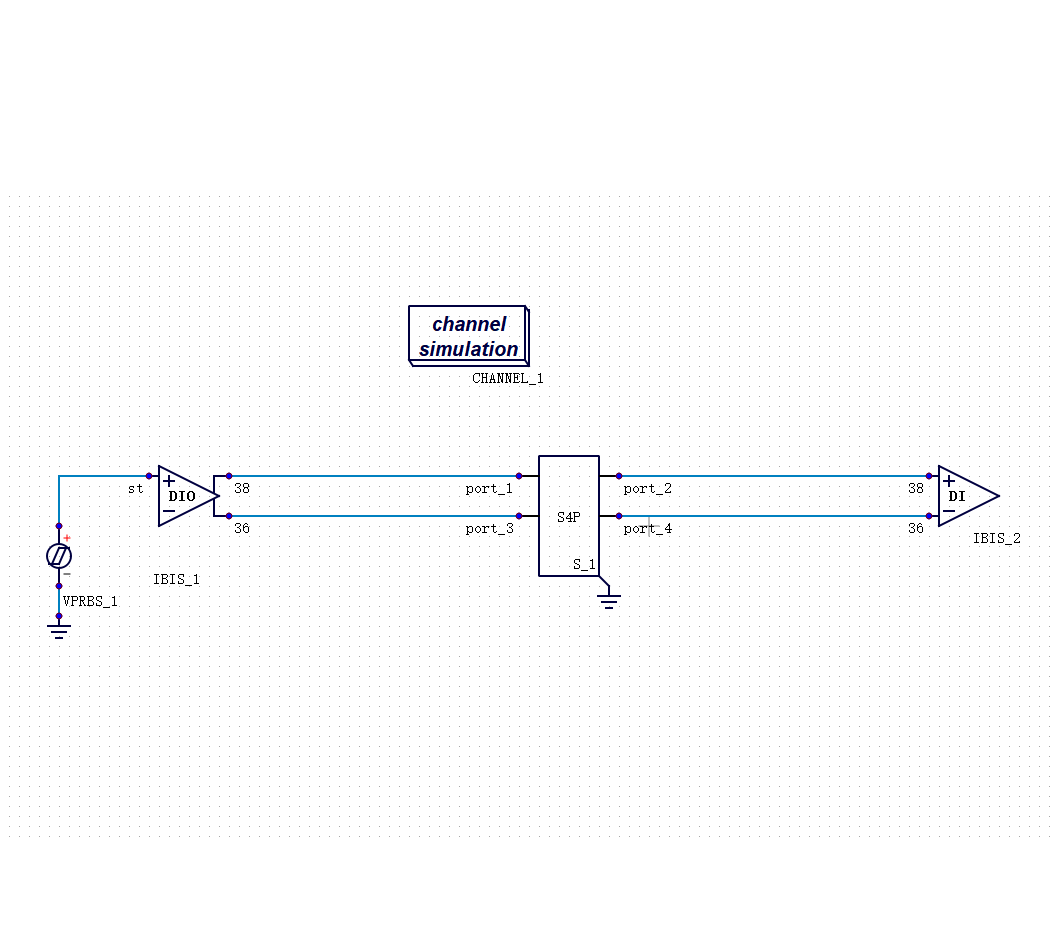

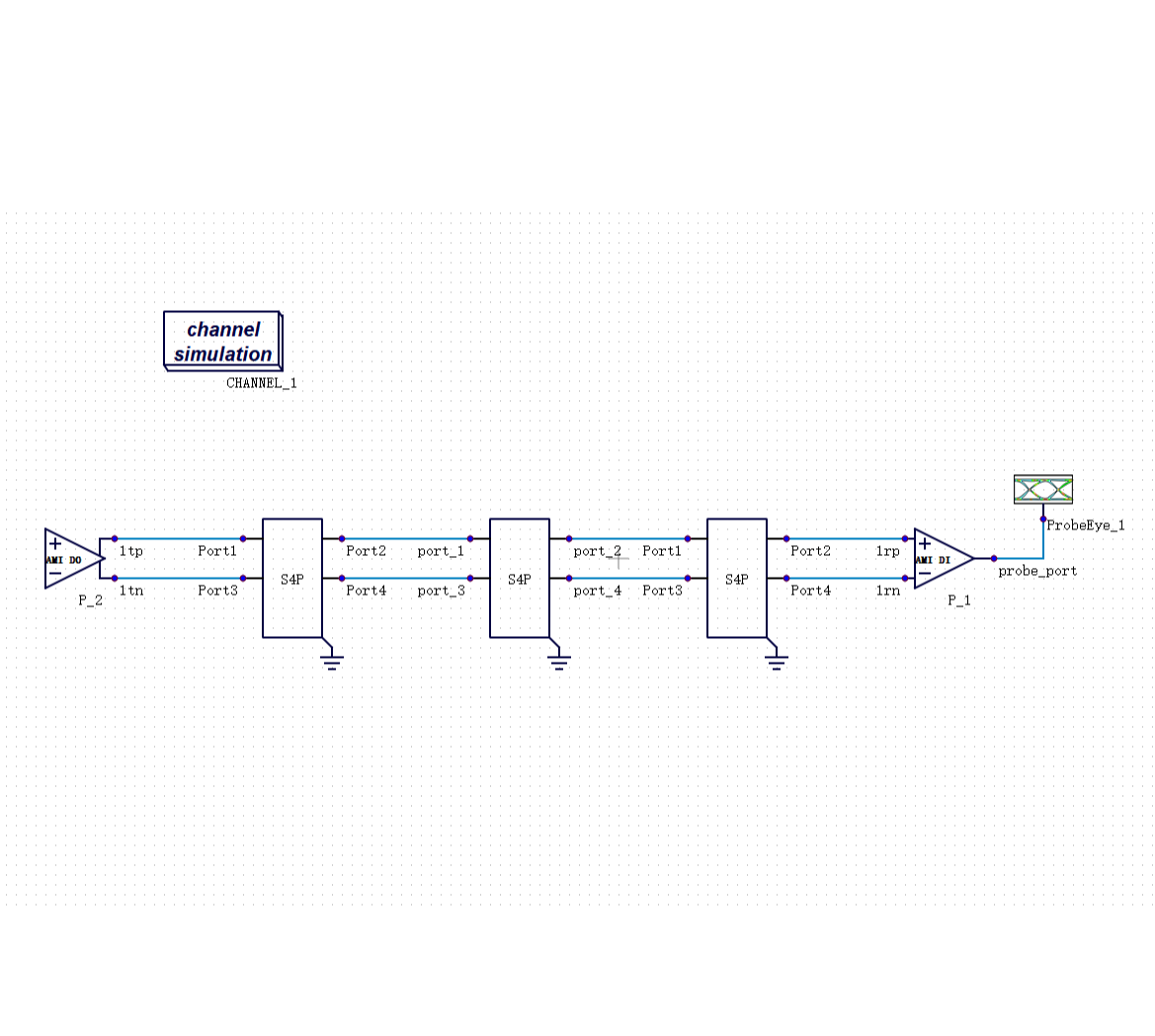

SIDesigner 是一款基于图形化交互界面的信号完整性仿真工具。它支持常见的电路元件类型组成的通用电路仿真。通过快速假设分析,以获得在预布局阶段从信号完整性和电源完整性角度最佳布局决策。借助第三方 3D 全波建模求解器,它可完成所有信号完整性时序签核仿真工作。为应对 5G/AI 高吞吐量和带宽要求,软件提供了高速 SerDes 和 DDR 类型的仿真功能。工程师可以对电子系统进行全面的系统性能评估、优化系统可靠性及稳定性,加速产品研发、迭代过程。

产品功能

-

易于掌握的 GUI 界面

简单的原件和导线布置

结构层次设计

端点和器件的注释

自定义窗口结构背景

智能的点对点布线

-

-

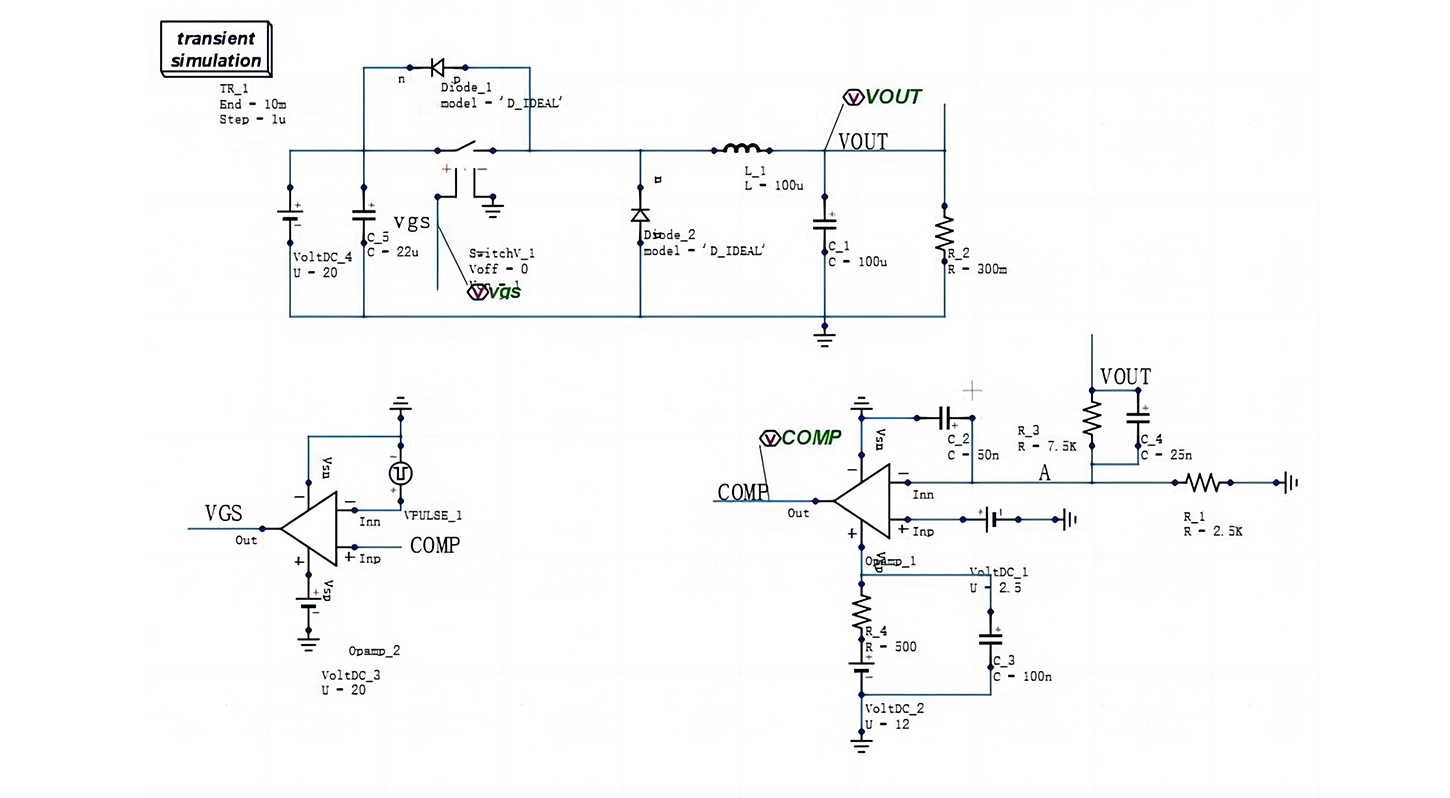

强大的内置 SPICE 引擎

快速模拟仿真

复杂电路的高效收敛

复杂电路的高效收敛

-

-

支持的电路元件

R、L、C、E、F、G、H

传输线,过孔

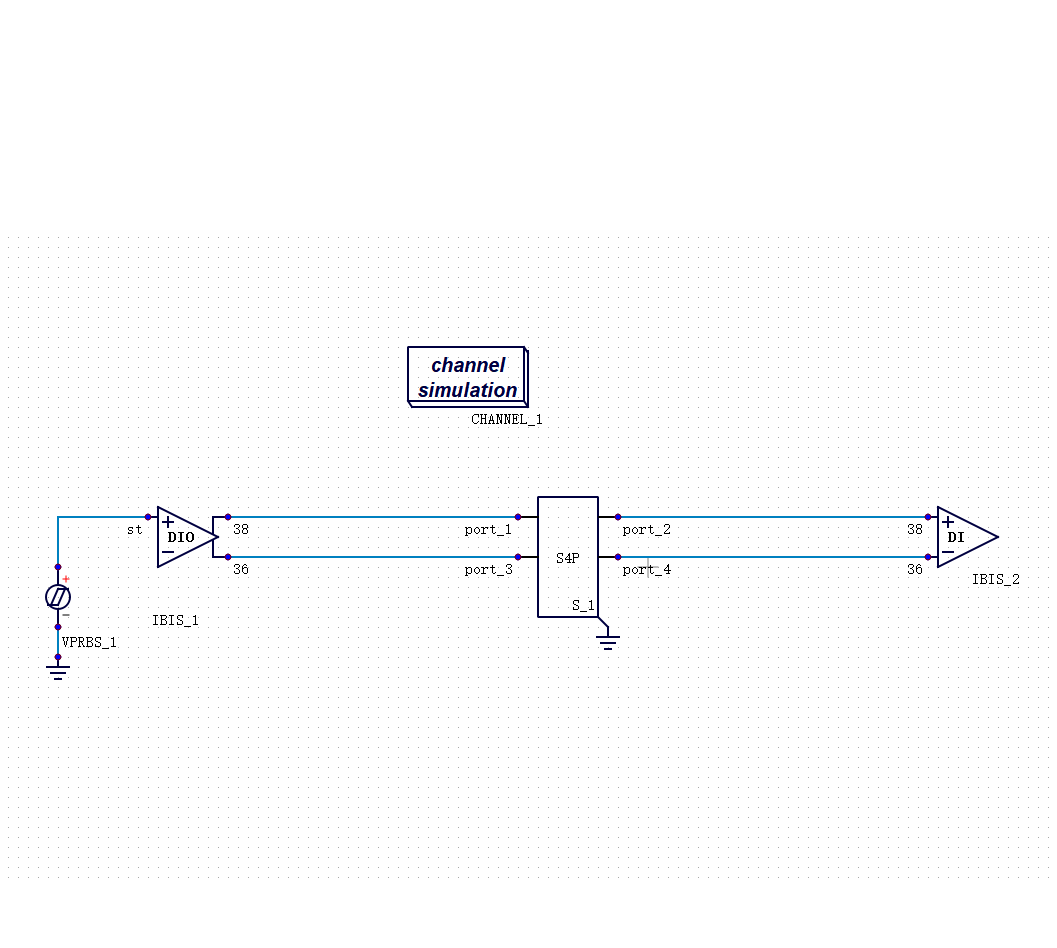

S 参数/宽带 SPICE 模型

IBIS, IBIS-AMI

支持用户导入子电路

常用信号源

-

-

支持的分析类型

静态工作点(直流偏置点)分析

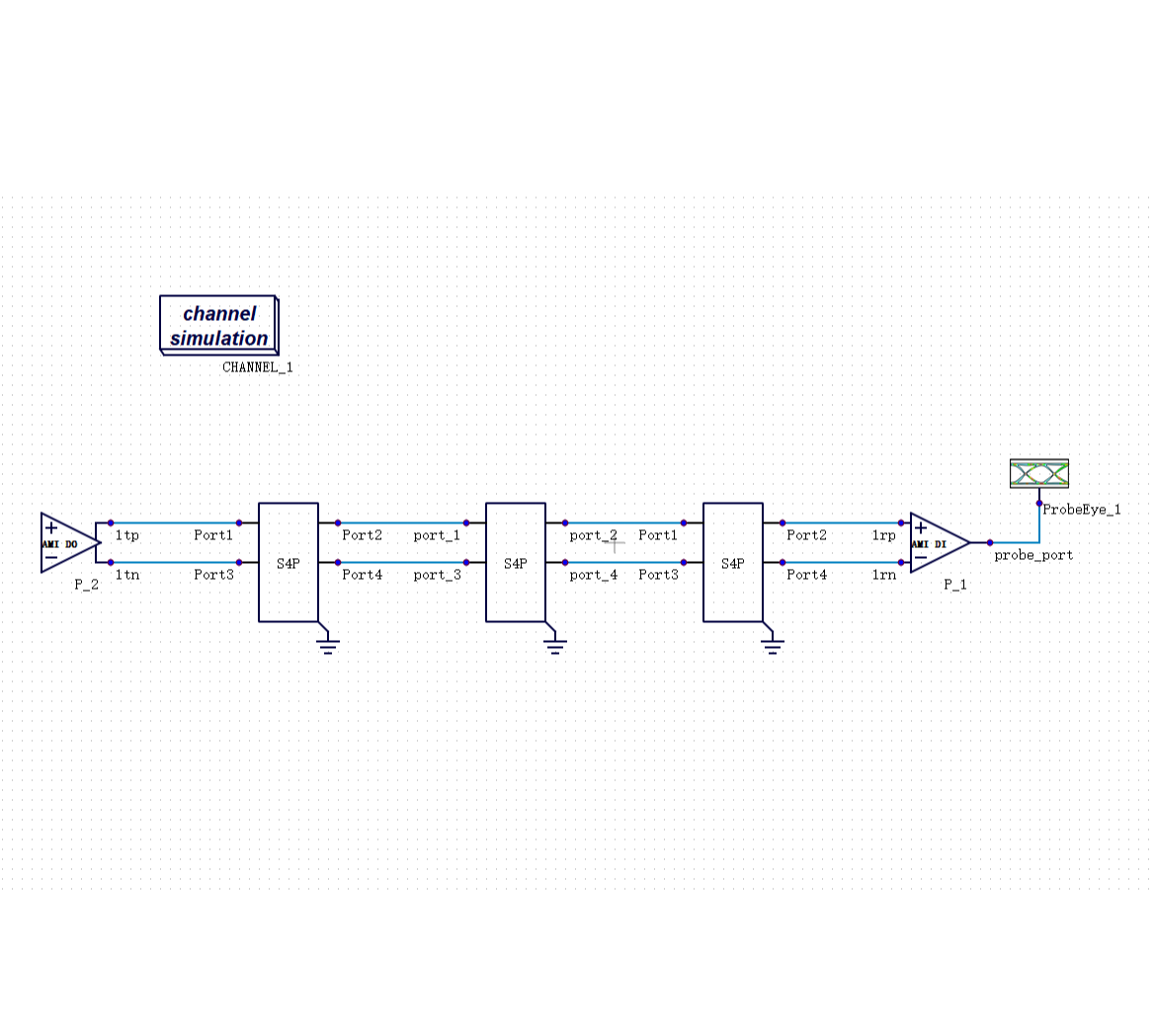

无源通道仿真

DC 分析

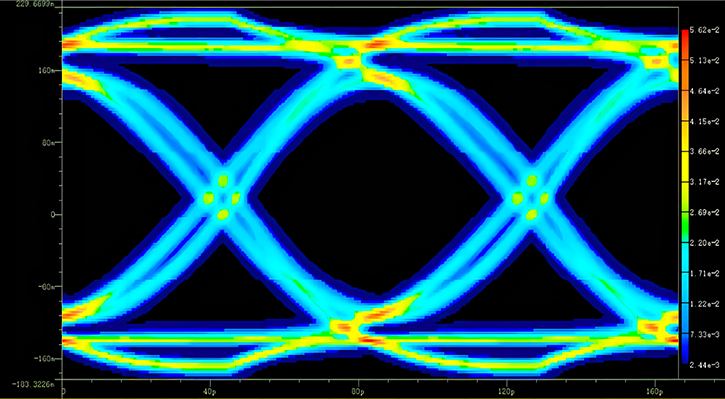

统计学眼图分析

AC 分析

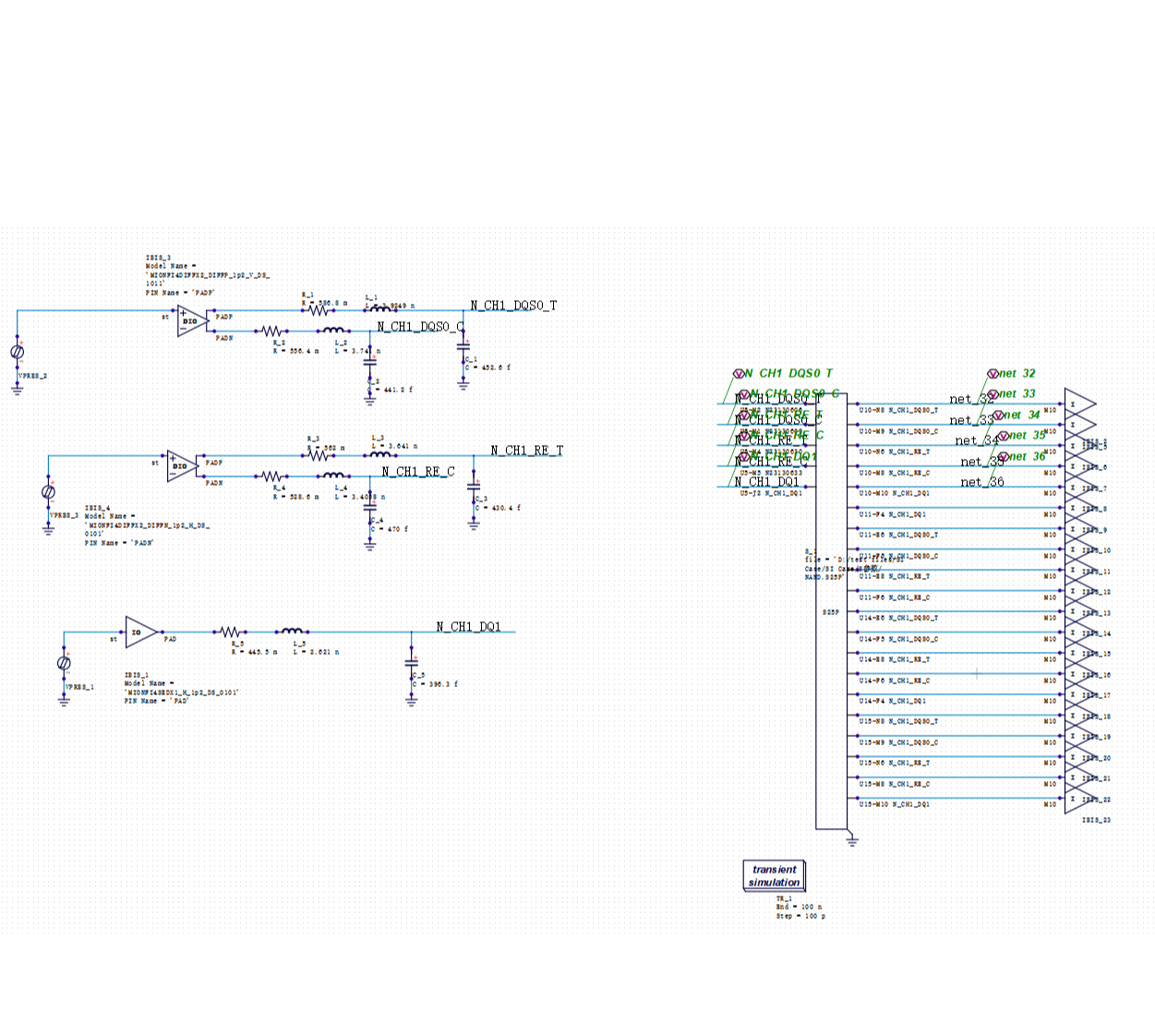

瞬态分析

PDA(最大值失真分析)

Bit by bit 分析

-

-

内置波形查看器

可以快速查看及测量仿真结果

-

视频演示

-

SIDesigner的基础页面操作

SIDesigner的基础页面操作 -

SIDesigner的S参数简单导入与引脚调整

SIDesigner的S参数简单导入与引脚调整 -

DFE功能演示

DFE功能演示

特点优势

-

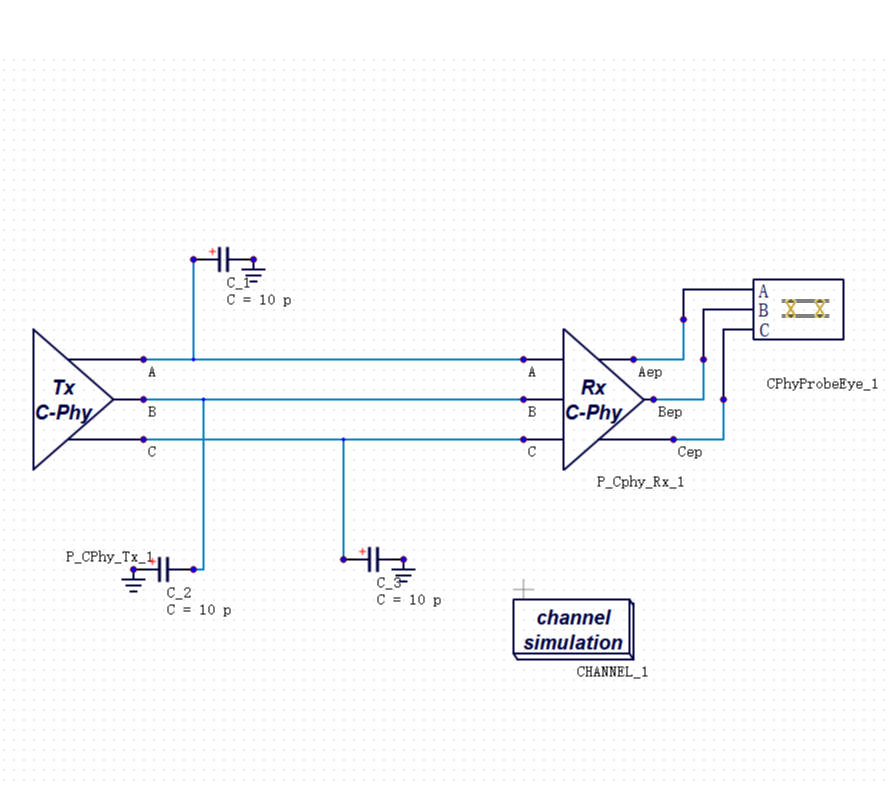

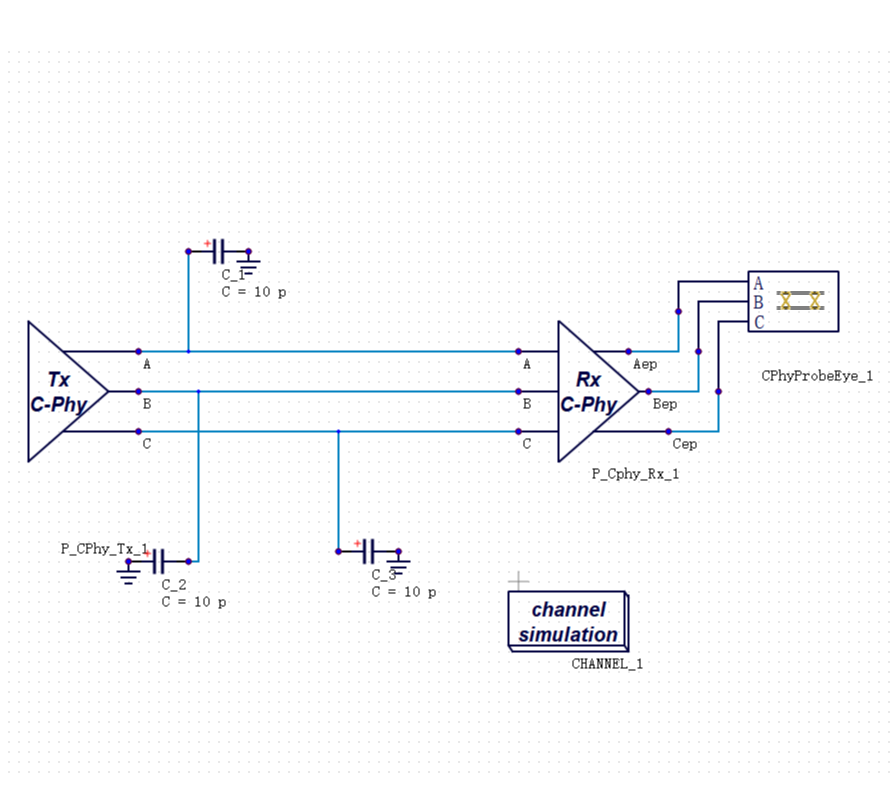

全方位的模型支持

IBIS4.1/4.2/5.X、巴伦等单端差分变换元件、AMI模型支持、多端口S参数、宽带spice模型、芯片晶体管模型(CMOS工艺 BSIM模型 、StarRC输出的晶体管寄生参数文件 .spi .spf、 子电路文件ckt inc lib等)、有损、无损微带/带状线/Cable模型,铜皮粗糙度模型(包括且不限于W Element)、NRZ,PAM4,CPHY信号源、过孔模型、多die合封的器件模型 *.EBD、文件作为激励源。

-

高速串行接口

高速串行接口

-

广泛的行业应用

广泛的行业应用

-

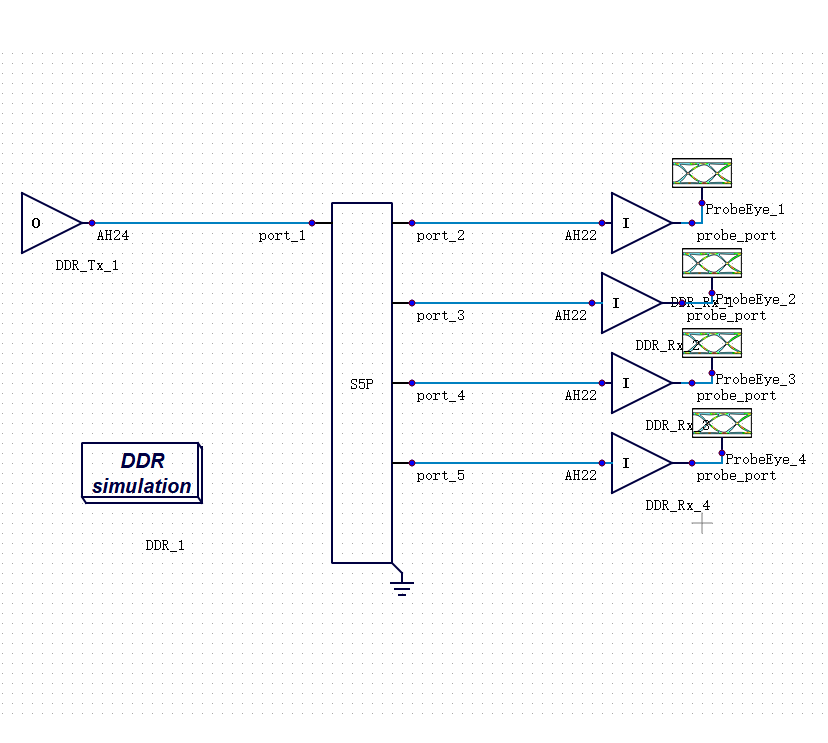

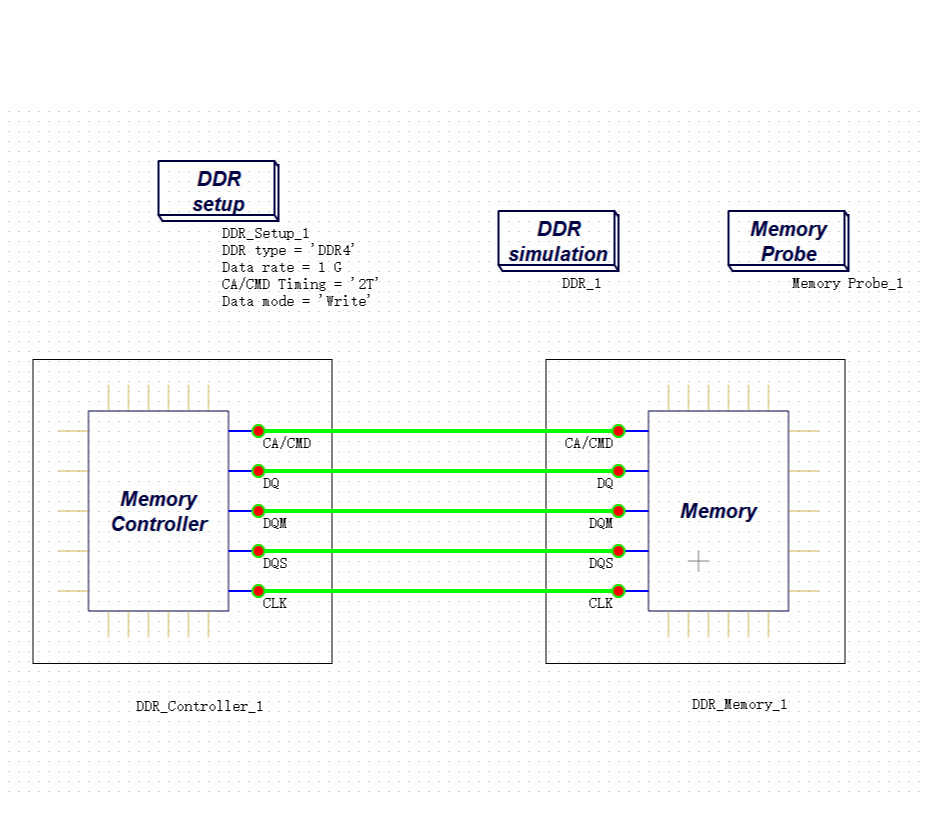

高速并行接口

高速并行接口

-

强大的二次编程功能

强大的二次编程功能

产品价值

-

帮助客户提前发现问题

通过仿真,设计师可以在设计阶段就预见到可能的信号完整性问题,如信号反射、串扰、噪声等,而无需等到实物制作出来再进行调试,大大节省了时间和成本。

-

帮助客户优化设计

仿真软件可以帮助设计师调整PCB布局、布线、阻抗匹配等参数,优化设计,确保信号传输的高质量和高速度。

-

帮助客户提高产品质量

通过仿真优化后的设计,产品在实际使用中的性能更稳定,故障率更低,从而提高客户满意度。

-

帮助客户提供标准化和可重复性

仿真软件通常具有标准化的工作流程和结果分析,使得设计过程更加规范,结果可重复验证,提高设计的可信赖度。

-

帮助客户加速产品上市时间

通过减少设计迭代次数,缩短设计周期,加快产品上市速度,提升市场竞争优势。

-

帮助客户节省成本

通过提前发现问题和优化设计,可以避免因设计错误导致的材料浪费和返工成本。

相关场景

-

UFS 3/4

UFS 3/4主要解决数码相机、智能电话等消费电子产品使用的闪存存储。在提供高数据传输速度和稳定性的同时,也可以减少消费者对于市面上各种存储卡格式的混淆和不同存储卡转接器的使用

-

eMMC

eMMC主要应用于嵌入式储存媒体比如智能型手机及平板计算机等消费类智能型移动装置上

-

HDMI

HDMI主要应用在高质量的音视频传输

-

DPHY

DPHY主要应用在包括连接摄像机,音频,存储,RF和提供芯片到芯片的处理器间(IPC)通信

-

LPDDR 3/4/5

LPDDR 3/4/5主要应用于移动设备和嵌入式系统等需要长时间使用的场景,比如手机、平板电脑

-

MPHY

MPHY主要应用在包括连接摄像机,音频,存储,RF和提供芯片到芯片的处理器间(IPC)通信

-

MIPI

MIPI主要应用在移动设备接口

-

CXL

CXL主要解决大内存的问题

-

CPHY

CPHYCPHY主要应用在移动设备中高传输速率

-

DDR 3/4/5

DDR 3/4/5主要应用于计算机、服务器和其他高性能计算设备等领域

-

NAND

NAND主要应用在大容量数据存储,如智能手机、PC、平板电脑、U 盘、固态硬盘、服务器等领域

-

PCIe 4/5/6

PCIe 4/5/6主要是显卡、网卡、存储设备等通过PCIe接口,设备之间可以进行高速通信,从而提高数据传输效率和传输速度

相关行业

-

通讯行业

5G+时代来临,高速传输对芯片之间通信速率的提升以及网络速率升级提供有力支撑。通信芯片上超高速信号的传输对信号完整性的仿真尤为重要,巨霖工具助力行业客户提升设计效率、把控验证质量。

-

存储行业

DDR3/4/5,LPDDR3/4/5协议读写速率阶梯上升,行业标准的高速存储器具有广阔市场前景,高精度的超高速读写信号仿真至关重要。巨霖工具助力行业客户提升设计效率、把控验证质量。

-

大数据中心GPU行业

信息时代来临,海量数据填充人们的日常生活,数据中心提供包括存储、数据管理、数据处理和传输在内的功能,是大规模高性能计算和海量数据存储的重要实体,为信息化建设提供强有力的支撑,数据中心的大容量、大带宽、大算力、低时延、高能效、高可靠等重要的性能指标要求信息传输和处理要以极快的速度和高精的质量完成,这就需要更加精准、聚焦信号完整性的高速仿真。

-

物联网行业

物联网将物理世界中的各种“事物”与互联网连接起来,通过智能设备、传感器等收集数据,然后通过网络进行信息交换、处理和存储,以实现智能化管理和控制。在5G+时代,物联网将依托移动网络的规模效应支撑未来的千亿物联,超高速信号和超大带宽背后是更准确的信号完整性仿真需求。

-

产品详情

-

产品功能

-

视频演示

-

特点优势

-

产品价值

-

相关场景

-

相关行业