Julin-Tech Hosts Inaugural SI/PI High-Level Tech Seminar

-

2026.01.26

Currently, high-speed interface technology is undergoing a generational leap: DDR6 speeds have reached 17.6Gbps, UCIe 3.0 has pushed to 64Gbps, and SerDes is evolving toward the 224Gbps limit. This exponential surge in transmission rates presents unprecedented challenges for Signal Integrity (SI) design, particularly in Bit Error Rate (BER) metrics, complex equalization algorithms, and margin optimization.

In response to these industry pain points, SI engineers must gain a profound understanding of underlying algorithms to break through design bottlenecks, while EDA companies need to refine product logic to align precisely with real-world requirements. On January 23, 2026, julin-tech successfully hosted its first SI/PI High-Level Tech Seminar at its headquarters. The event brought together technical experts from leading enterprises in semiconductor design, core storage, intelligent terminals, and New Energy Vehicles (NEV) to join the julin technical team in exploring simulation hurdles within the context of this generational shift.

Understanding the "Core" of EDA Tools

Jiaxin Sun , Founder and Chairman of julin-tech, stated in his opening remarks: "As an EDA tool provider, we must ensure our tools are not only accurate but also 'insightful.' We need to understand the user's design flow and their actual pain points. This is the original intention of this seminar: to facilitate exchange across three levels—exploring challenges brought by frontier technologies, solving pain points in practical design flows, and showcasing julin’s technical expertise in high-speed interface simulation."

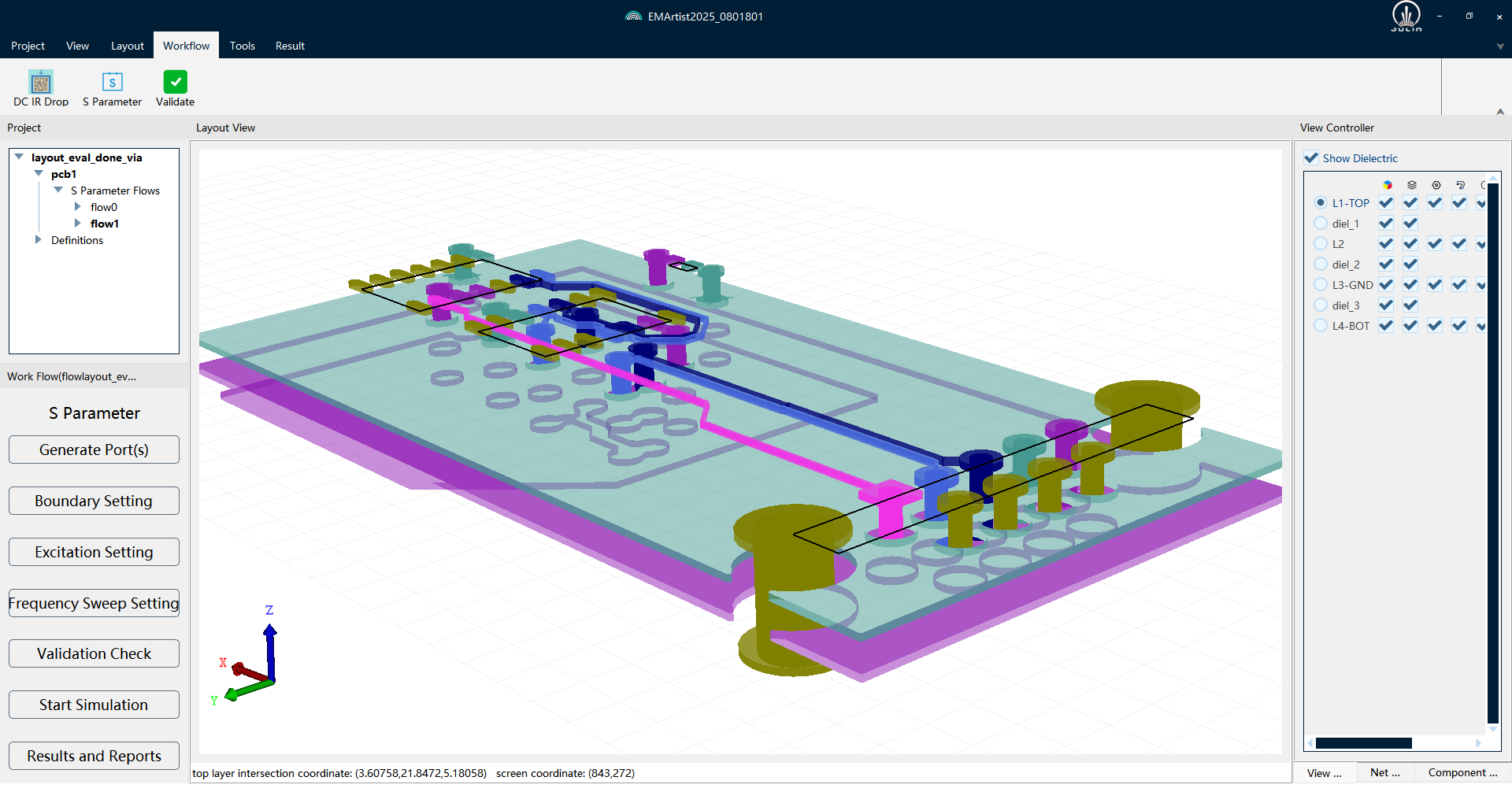

Subsequently, Mr. Sun delivered a keynote speech titled Mathematical Challenges in EDA Software. He pointed out that the core algorithms at the bedrock of EDA software reflect a deep integration with computational and applied mathematics. To solve "chokehold" technical restrictions, one must start from the mathematical foundations. julin remains committed to a 100% self-developed R&D model, aiming to break simulation bottlenecks in current high-speed designs at the source.

Deep Collaboration and Practical Insights

During the event, Junyong Deng, Vice General Manager of julin-tech, and Jialong Dong, Director of Technical Support, engaged in in-depth discussions with customers and industry partners regarding product applications and technical evolution. By communicating directly with frontline engineers about functional requirements and improvement suggestions, the julin team gained further insights into practical scenarios, providing a decisive basis for future product iterations and deep technical synergy.

The seminar featured compelling presentations from guests across the supply chain, including system communications, storage technology, and EDA industrial software, focusing on core dimensions such as underlying channel simulation algorithms, storage evolution, server design pain points, and link equalization optimization:

Mr. Fu, Senior Director at Longsys: "In the data-driven era of information explosion, higher performance, larger capacity, and competitive costs are the core drivers of storage evolution. NAND storage is undergoing a full-dimensional capacity upgrade from the cell level to the board level. Facing complex challenges such as high I/O capacitance and crosstalk in signal simulation, we persist in seeking optimal solutions within multiple constraints to drive the implementation of storage solutions through technical innovation."

Mr. Chen, Technical Expert at ZTE: "In the LLM (Large Language Model) era, the core challenge for AI servers lies in building a truly lossless network. Significant variances in hardware quality can be unpredictable; even a 0.1% packet loss can lead to a 50% loss in computing power. We must overcome the difficulty of evaluating a 1E-15 BER at the 112G (and higher) physical layer and achieve an extreme balance between accuracy and efficiency in DDR5 and PI simulation to ensure the stability of computing power under 10,000-card clusters."

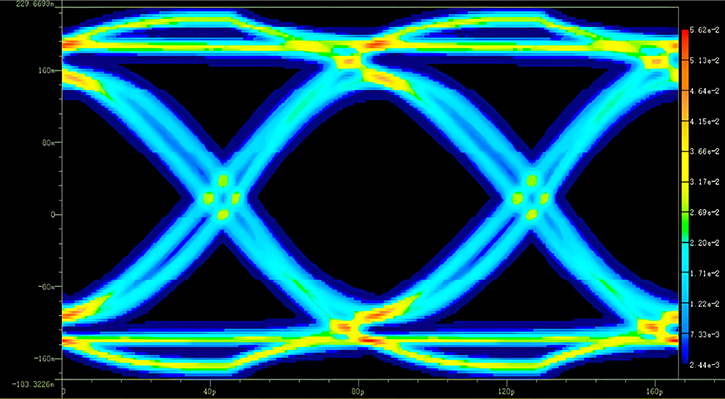

Mr. Zhang, Technical Expert at ZTE: "Eye diagram asymmetry is a comprehensive reflection of high-speed systemic issues, primarily caused by Inter-Symbol Interference (ISI) triggered by channel frequency response. To counter high-frequency attenuation, we utilize transmitter pre-emphasis and receiver Continuous Time Linear Equalization (CTLE) for precise compensation, combined with Decision Feedback Equalization (DFE) to suppress noise without amplifying high-frequency interference. Optimizing the eye diagram requires a combination of time-domain, frequency-domain, and statistical analysis."

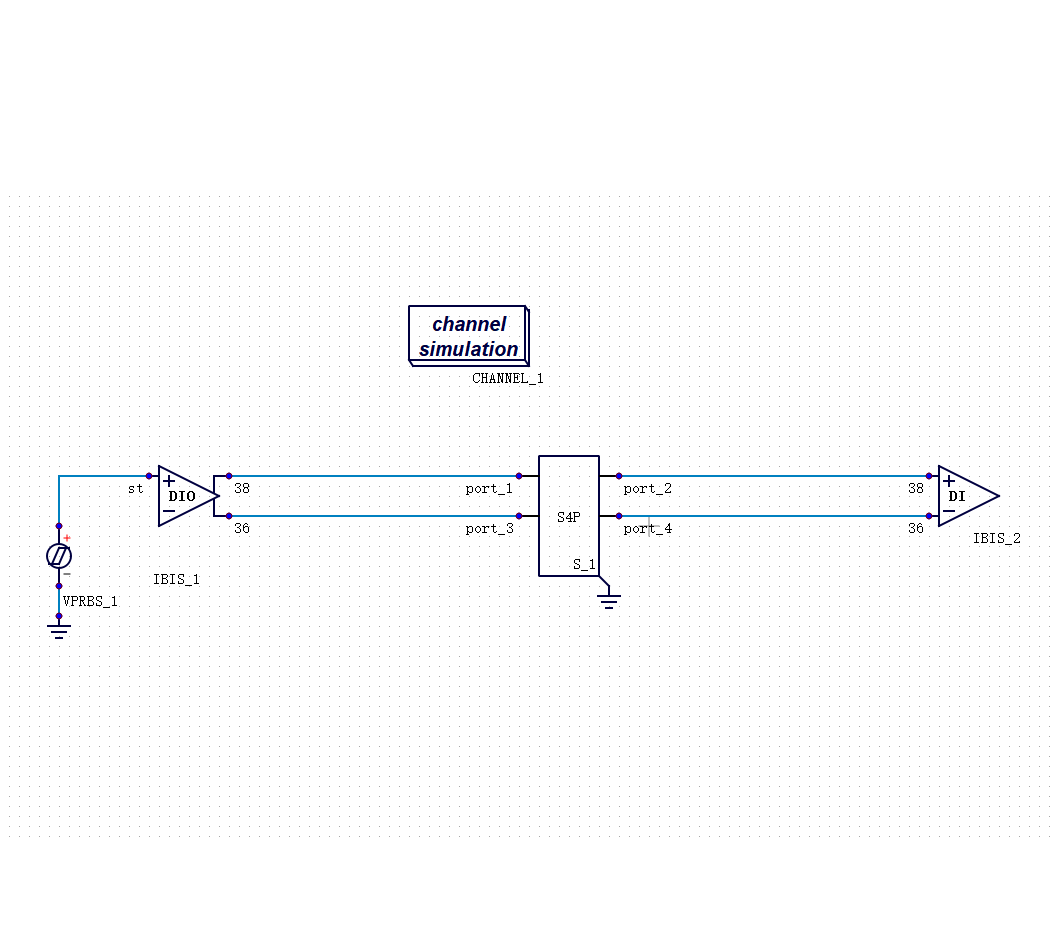

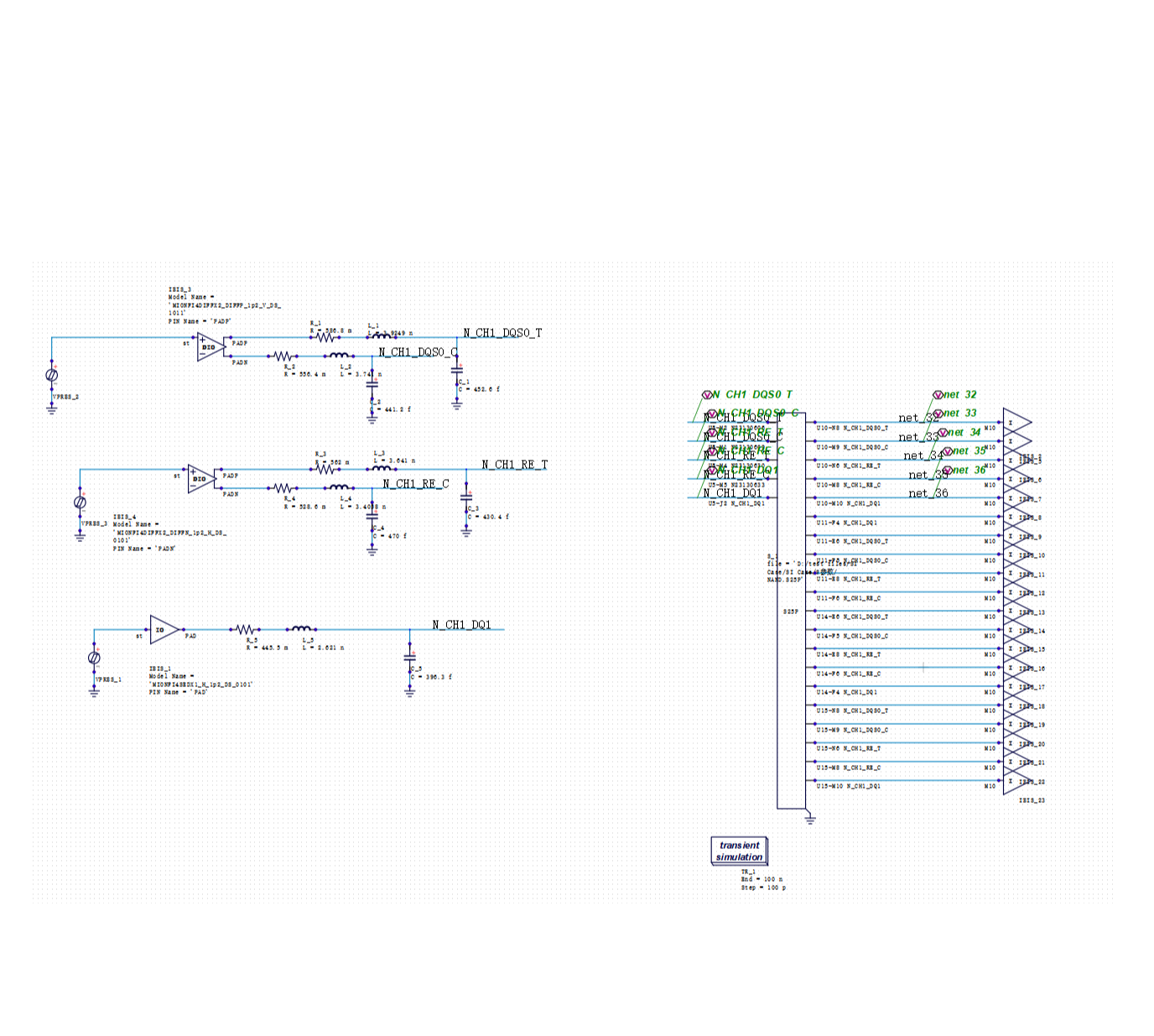

Jialong Dong, Director of Technical Support at Julin:“Moving towards a high-speed era, traditional simulation methods are facing an unprecedented crisis of confidence. We have found that the efficiency bottleneck of Transient Sim and the lack of accuracy in Channel Sim when handling complex crosstalk have become unavoidable systemic problems. When the old experience margin is squeezed to the limit by physical constraints, developers should no longer seek a sense of security in incomplete models. Only by breaking with convention and reconstructing the verification process or exploring new simulation algorithms can we build a truly high-confidence 'foundation' for high-speed design in complex physical channels.”

Junyong Deng, Deputy General Manager of Julin:“With the increase in interface speed and the shrinking margin, SI Signoff is facing the ultimate challenge of accuracy and efficiency. We cannot blindly rely on a single process, but should promote the deep integration of 'transient simulation' and 'channel algorithms'. In the future, SI/PI simulation will evolve towards automated turn-key solutions, empowered by AI technology and domestic substitution, to achieve a leap from 'imitation' to 'leading'.”

Recommended

-

Julin-tech Wins "China IC Design Achievement Award: EDA Company with Annual Technical Breakthrough" for the Third Consecutive Year2026.04.02

Julin-tech Wins "China IC Design Achievement Award: EDA Company with Annual Technical Breakthrough" for the Third Consecutive Year2026.04.02 -

Julin-Tech Hosts Inaugural SI/PI High-Level Tech Seminar2026.01.26

Julin-Tech Hosts Inaugural SI/PI High-Level Tech Seminar2026.01.26 -

Joint Project of Julin Technology and Southeast University Wins First-Class Engineering Technology Award of the Ministry of Education2026.01.06

Joint Project of Julin Technology and Southeast University Wins First-Class Engineering Technology Award of the Ministry of Education2026.01.06 -

At ICCM 2025, Jiaxin Sun from Julin Technology States: "Mathematics is the Only Precise Language for 'What You Simulate Is What You Get'"2026.01.05

At ICCM 2025, Jiaxin Sun from Julin Technology States: "Mathematics is the Only Precise Language for 'What You Simulate Is What You Get'"2026.01.05