Selecting SI Simulation Tools: Practical Verification of SIDesigner's 4 Core Capabilities

-

2026.04.29

In our previous discussion, we established four critical benchmarks for selecting a Signal Integrity (SI) tool. Now, we answer the ultimate question: Is there a tool on the market that hits all four? The answer is SIDesigner. Let’s break down how it validates these standards in real-world scenarios.

Standard 1: A High-Precision "Safety Net" Path

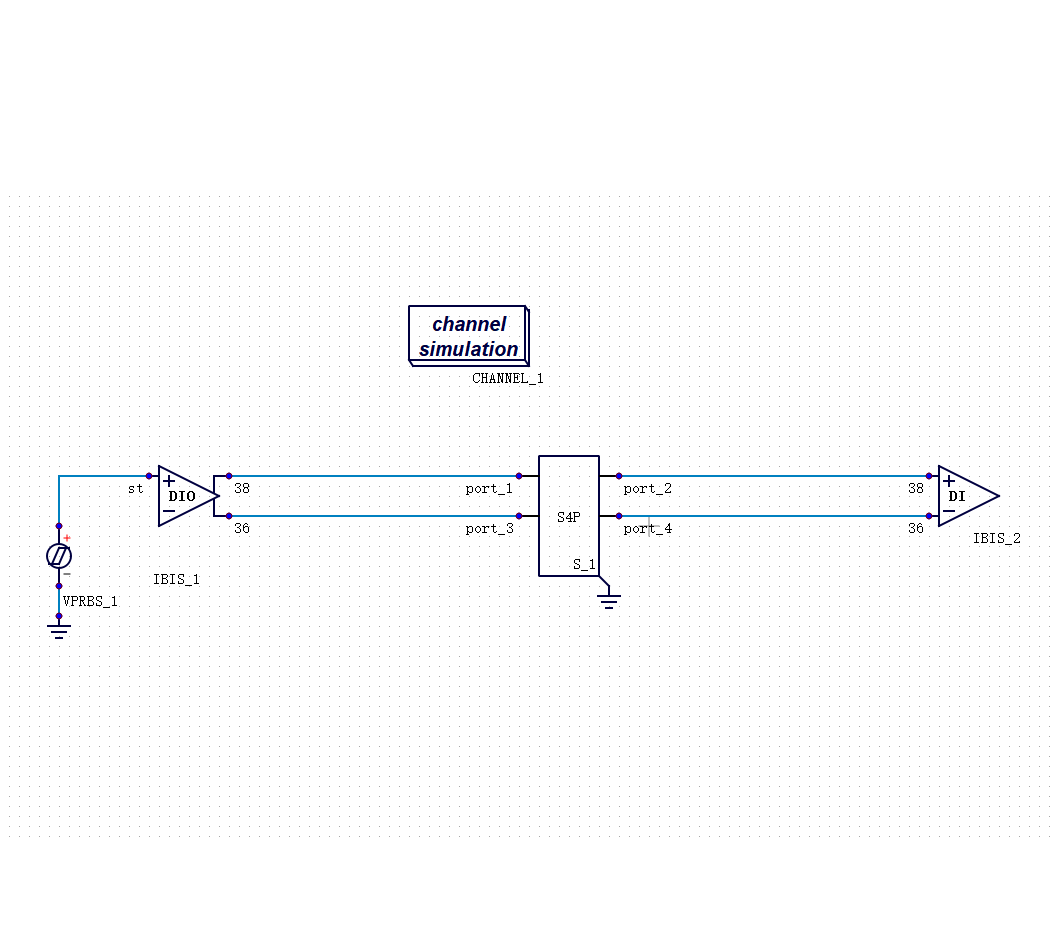

SIDesigner is built on the self-developed SIDCore engine. Beyond standard statistical channel simulation, it features an integrated True-SPICE path as a high-precision alternative.

While IBIS macromodels are excellent for speed, their approximation errors can exceed the design margin itself when working at the edge or under extreme PVT (Process, Voltage, Temperature) corners.

The Solution: SIDCore’s True-SPICE path performs high-fidelity time-domain simulations directly on the channel.

The Benefit: It doesn’t rely on the linear approximations of macromodels, matching industry "Golden" standards for accuracy.

Seamless Switching: Use statistical simulation for rapid iterations and flip to True-SPICE for final verification—all in one environment without re-modeling.

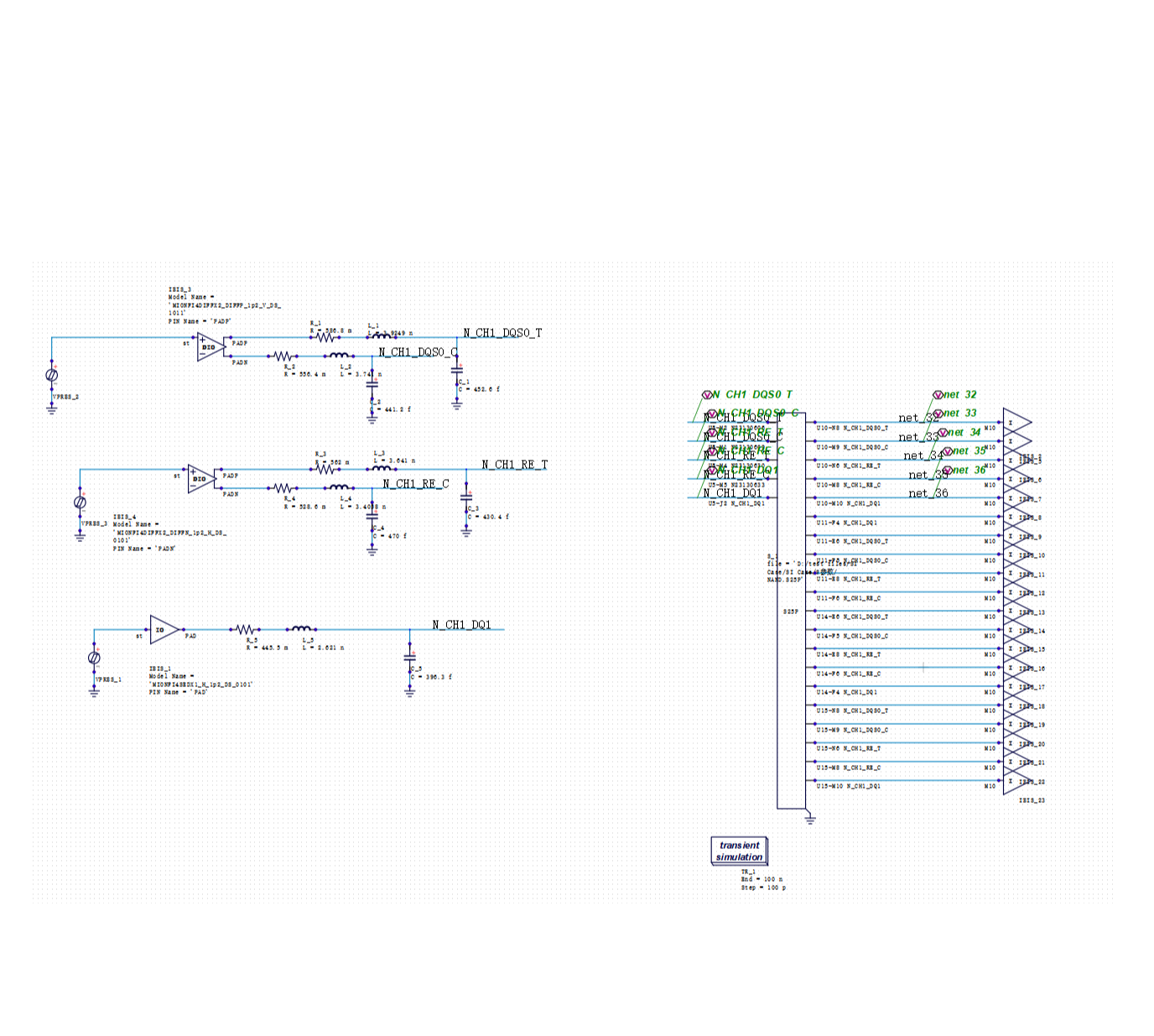

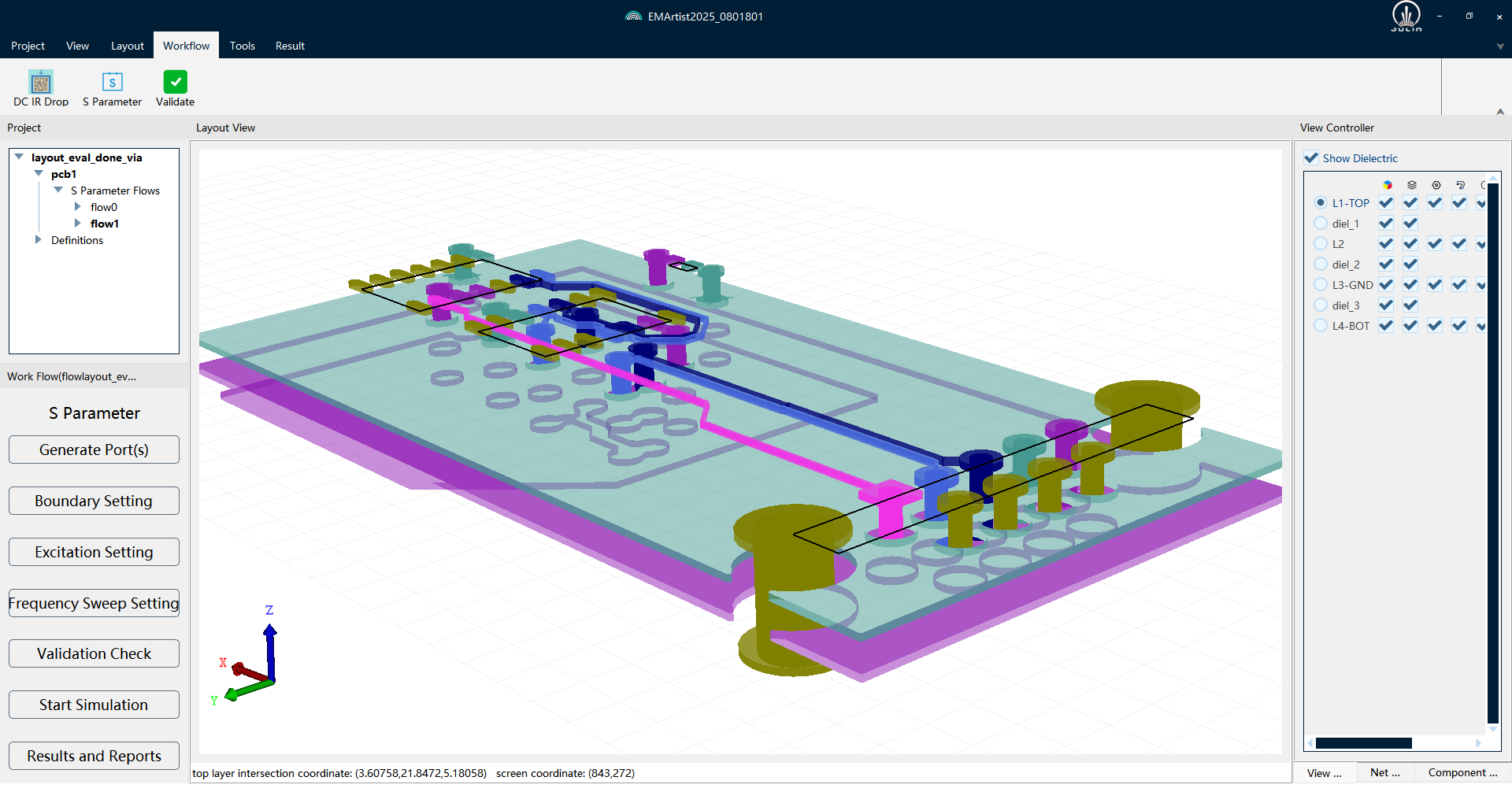

Standard 2: Chip-Package-Board Co-Simulation

From its inception, SIDesigner was positioned as a one-stop SI/PI sign-off platform for the entire system.

Instead of simulating components in isolation and stacking the results, SIDesigner integrates Chip I/O models, Package parasitics, and PCB transmission lines into a single environment. This preserves critical coupling effects:

Interaction Tracking: Capture the interplay between package parasitic inductance and chip I/O drive strength.

Reflections: Directly observe reflections at package pins caused by PCB impedance discontinuities.

Applicability: Essential for high-speed parallel interfaces like DDR5, HBM3, and UCIe, as well as serial interfaces like PCIe 6.0 and USB4.

Standard 3: Dual-Path Support (Statistical & Transient)

The SIDCore engine offers a "dual-engine" approach to prevent the "accuracy trap":

Channel Simulation (Statistical): Rapidly scans vast parameter spaces, perfect for early-stage design iterations.

True-SPICE (Transient): Provides a time-domain precision baseline, essential for margin confirmation and non-linear scenarios.

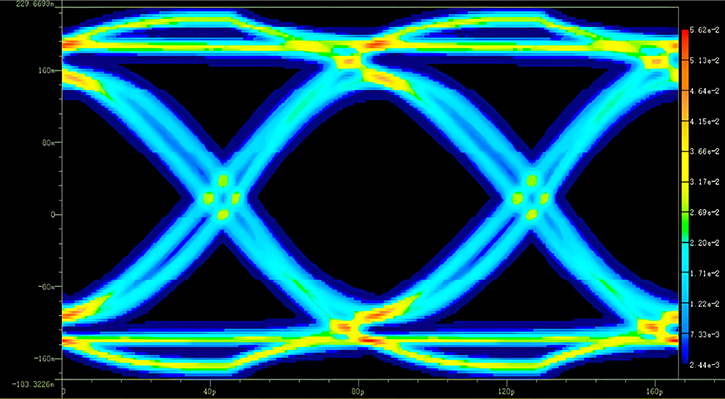

The Reality Check: In a DDR interface EQ scenario, the statistical method (at BER = 1*10-6) calculated an eye width of 260ps, while the Long Transient benchmark measured 362ps. That 28% discrepancy is the difference between a "Pass" and a "Fail" at sign-off.

SIDesigner doesn't force you to choose. If statistical results are questionable (e.g., in non-linear DFE scenarios), you switch to the transient path for a definitive answer.

Standard 4: Full-Workflow Platform Integration

From AC analysis and channel simulation to eye-diagram post-processing and batch DOE (Design of Experiments) scans—everything happens in one place.

Eliminating Hidden Errors: Data format conversion and inconsistent parameter settings between different tools are major sources of invisible errors. A unified platform eliminates these at the source.

Efficiency: In specific scenarios, SIDesigner can improve verification efficiency by over 10x.

Integration: Supports customization and integrates easily with mainstream design tools and existing verification flows.

Real-World Case Studies

1. DDR Interface DFQ Optimization

A leading memory chip company used SIDesigner's built-in DFQ (Design for Quality) module to optimize a DDR interface. By performing multi-parameter co-optimization, they reduced the defect rate from 13.8% to 7.6% with virtually zero loss in eye height or width.

2. SerDes RSFEC BER Simulation

As rates climb toward 56/112/224G, PAM4 signals combined with DFE equalization make error propagation a major hurdle. RSFEC BER simulation is now mandatory.

Validation: A top IC design house verified that SIDesigner’s results for KP4 and KR4 FEC configurations align perfectly with theoretical expectations across the entire Pre-FEC BER range.

Third-Party Benchmark Results

A tier-one chip design firm conducted an independent evaluation of SIDesigner. Here are their conclusions:

Feature Performance vs. Golden Tool

Statistical Eye Diagram Highly consistent, even in complex TX jitter amplification scenarios.

Negative Eye Height Identical results (SIDesigner retains raw data without "clipping").

Jitter Modeling Full modeling and simulation capabilities for jitter amplification.

Continuity High continuity in negative eye height calculations; no deviation from truncation.

Final Consensus: > "SIDesigner’s statistical eye algorithms meet all acceptance requirements for both accuracy and functionality, aligning with the highest industry standards. It is officially approved for production application."

Note: During testing, a competing commercial tool simply displayed "Not Supported" in the TX jitter amplification scenario.

Ready to Benchmark Your Design?

If you are evaluating SI tools for DDR5, HBM3, UCIe, or other high-speed interfaces, don't take our word for it—test it against your own project.

[Contact our technical engineers for a 1-on-1 demo]

Recommended

-

Selecting SI Simulation Tools: Practical Verification of SIDesigner's 4 Core Capabilities2026.04.29

Selecting SI Simulation Tools: Practical Verification of SIDesigner's 4 Core Capabilities2026.04.29 -

How to Choose DDR5/HBM3 Signal Integrity Simulation Tools? Four Verification Standards2026.04.23

How to Choose DDR5/HBM3 Signal Integrity Simulation Tools? Four Verification Standards2026.04.23 -

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20 -

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13