PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation

-

2026.03.20

I. Core Technical Highlights

·Signoff-Grade Device Precision, the Final True-Value Defense Before Tape-Out: Based on full physical transistor-level modeling, system-level comparative validation against industry Golden standard tools shows power node voltage errors reaching the Golden level. It has been recognized by Tier-1 (A1 class) customers as a Signoff-grade tool.

·Full Process Coverage with Native Support for 3rd-Gen Semiconductors: From mainstream CMOS (BSIM3/4, PSP), FinFET (BSIMCMG), SOI, and Bipolar, to SiC/GaN (Level 90/91 physical models jointly developed with Southeast University)—achieving exact device-level modeling for every process node, rather than relying on behavioral approximations.

·Fully Automated IP PVT Corner Verification for Visible Design Cycle Reduction: Under Signoff precision, automated matrix sweeping across Process × Voltage × Temperature (PVT) corners compresses traditional manual verification workflows from weeks to merely hours.

·Full-Link PDK Consistency, Unchanging Precision Baseline from Silicon Data to Signoff: As the core computational engine for modeling tools like IC-CAP, PanosSPICE permeates the entire flow: "Silicon Test Data → Device Model Extraction → PDK Verification → Standard Cell Library Characterization → Customer Design Verification," eliminating precision drift caused by tool switching.

At the critical juncture of ICs advancing towards advanced nodes and heterogeneous integration, simulation engineers face an unavoidable fundamental contradiction: True-SPICE precision is impeccable, but a single complex simulation often takes days; FastSPICE accelerates the process, but the loss in accuracy can directly lead to tape-out risks.

PanosSPICE's technical exploration is a systemic answer to this proposition at the device level.

II. From Silicon Data to Signoff: The Precision Infrastructure

PanosSPICE is not a single-point simulation tool, but a precision link connecting "measurement data" with "design confidence." Across this link, the exact same physical-level modeling baseline runs from beginning to end—meaning the computational results at any stage are traceable, reproducible, and perfectly aligned.

III. Core Technical Capabilities

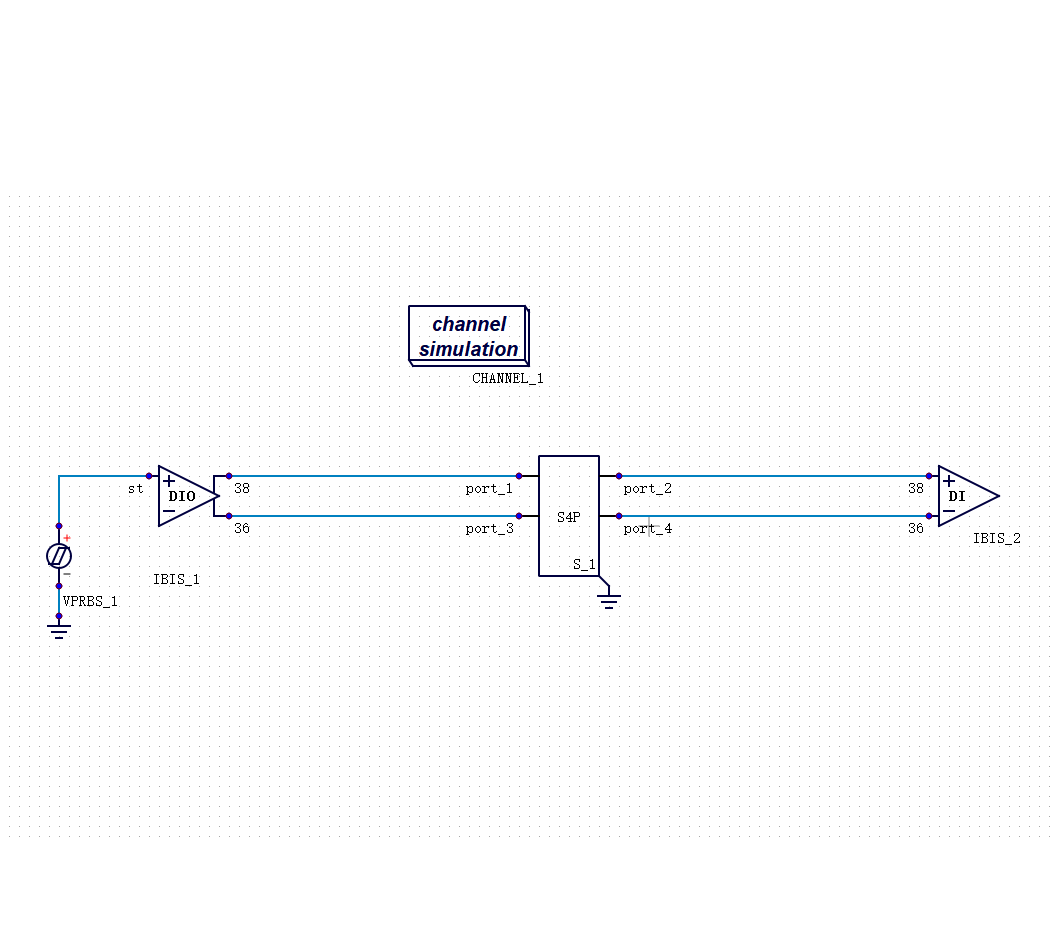

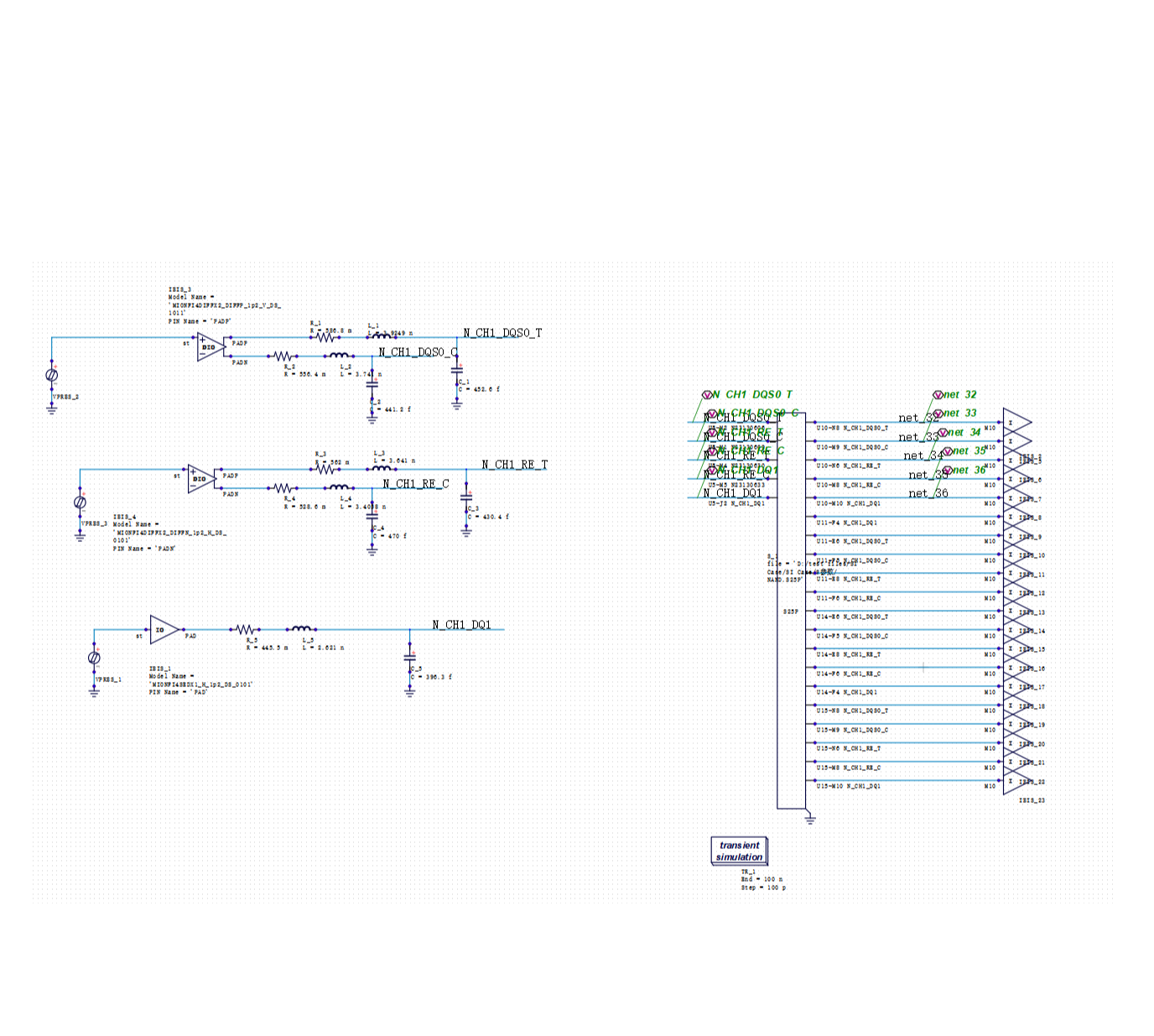

Power Integrity (PI) Verification: Quantified Cases

In Power Integrity (PI) analysis, PanosSPICE demonstrates a dual advantage in both precision and efficiency:

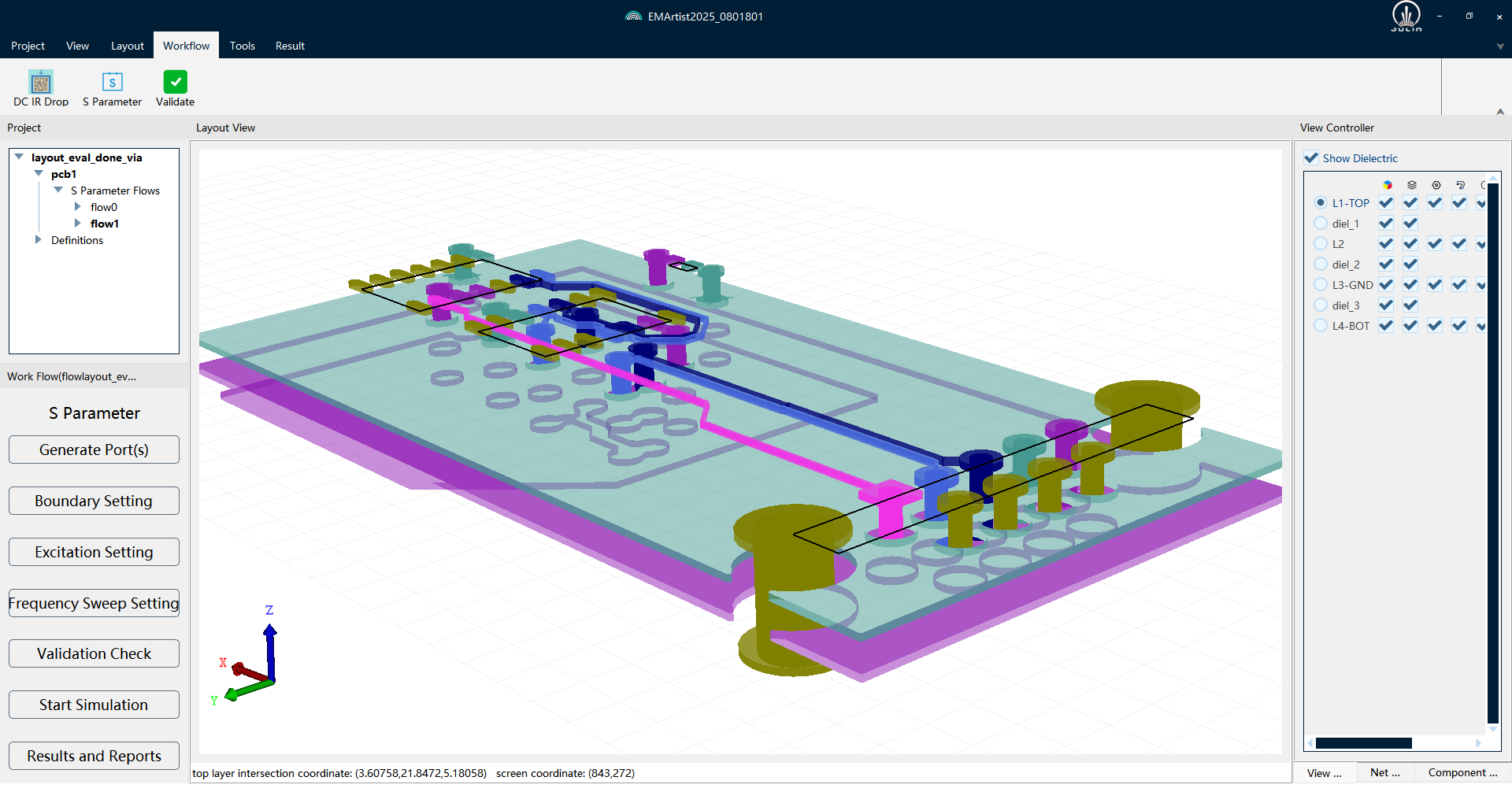

Precise Power Delivery Network (PDN) Modeling: Supports comprehensive modeling from on-chip PDNs to the package and PCB levels, accurately capturing key characteristics such as power noise, voltage drops, and resonance.

Real case studies:

Fully Automated IP PVT Corner Verification: Visible Efficiency

For IP development teams, PanosSPICE features built-in complete Measurement functions and Parametric Sweep capabilities:

·Parametric Sweep: Sets up the full Process × Voltage × Temperature matrix, driving fully automated batch simulations with a single click—eliminating manual, item-by-item configuration.

·Monte Carlo Statistical Analysis: Precisely quantifies the impact of process variations on key IP performance indicators, outputting yield distributions.

·Efficiency Comparison: Traditional manual iteration ("run once, tweak once") takes weeks; PanosSPICE fully automated PVT sweeps are completed in hours.

Applicable Scenarios: Cross-corner characteristic verification for various analog/mixed-signal IPs such as Op-Amps, ADC/DAC, LDO, PLL, SerDes PHY, and DDR PHY.

3rd-Gen Semiconductors: Native Modeling, Not Behavioral Approximation

SiC (Silicon Carbide) and GaN (Gallium Nitride) are accelerating penetration in fields like New Energy Vehicles (NEVs), power converters, and 5G RF. However, traditional SPICE tools generally lack native support for these new materials, often relying on behavioral model approximations, which limits prediction accuracy under extreme high-temperature and high-voltage conditions.

The Level 90/91 physical device models, jointly developed by PanosSPICE and Southeast University, achieve exact transistor-level modeling for SiC and GaN devices:

·Accurately captures switching transient characteristics (di/dt, dv/dt).

·Accurately predicts device behavior under extreme high-temperature (175°C+) and high-voltage conditions.

·Applicable for high-precision transistor-level simulation of AC-DC and DC-DC power conversion topologies.

Differentiated Value: This is currently the weakest area for competitors—most peer tools lack native physical models for SiC/GaN.

Verilog-A Mixed-Signal Simulation

Supports mixed simulation of Verilog-A behavioral models and transistor-level circuits within the same environment (compatible with Verilog-AMS LRM 2.40). During complex analog/mixed-signal IP verification, critical paths undergo precise transistor-level simulation while non-critical parts use simplified behavioral levels—achieving a dynamic balance between precision and efficiency without switching tools.

IV. Customer Evaluation and Certification

Tier-1 (A1 Class) Customer Acceptance Conclusion:

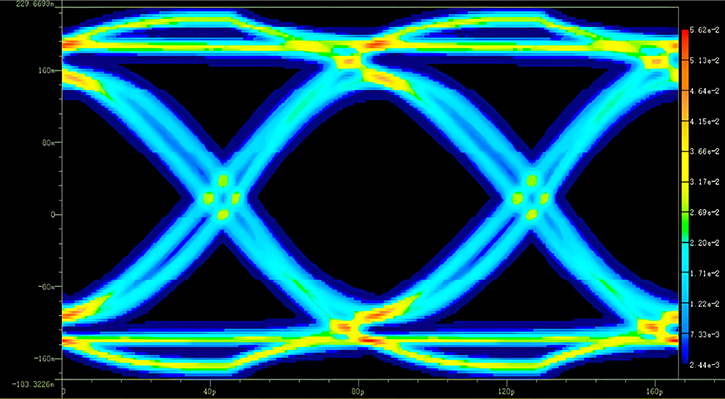

"This simulation tool operates stably in SI/PI analysis scenarios, with accuracy meeting the industry's Golden standard requirements. In multiple real-world project validations, Eye Width errors were controlled within 1.2%, and power node voltage errors were <5%. It has reached the standards of a Signoff-grade tool and can be stably applied in actual projects."

—— Acceptance Report from a Tier-1 (A1 Class) Customer

Engineering Application Value:

·Shorten Design Cycle: Fully automated IP PVT Corner verification compresses manual iteration workflows from weeks to hours.

·Reduce Tape-Out Risks: Golden-level precision guarantees design reliability.

·Lower Tool Costs: A unified platform reduces tool licensing fees.

·Enhance Team Efficiency: Eliminates the need to switch between multiple tools.

V. Technical Architecture: Unified Model System

PanosSPICE adopts a Unified SPICE Model architecture. A three-layer design achieves the unification of precision and universality:

Input Layer: Fully compatible with industry-mainstream SPICE netlist formats and syntax rules; existing design files can be imported with zero modifications.

Simulation Engine Layer: 9 major analysis engines covering comprehensive simulation needs—DC/OP, AC, Transient (LSP/SI), HPAC, HB (Harmonic Balance), POP (Power Integrity), Noise, Monte-Carlo, and Parametric Sweep.

Model Support Layer:

·Mainstream CMOS: BSIM3/4, PSP

·FinFET: BSIMCMG; SOI, Bipolar (VBIC, etc.)

·3rd-Gen Semiconductors: SiC/GaN Level 90/91 (jointly with Southeast University)

·Coverage spans from 28nm to advanced process nodes.

VI. Application Scenarios

High-Speed Digital: Full PVT Corner verification for high-speed interface PHY circuits like DDR5/6, PCIe, and SerDes; Transistor-level modeling for IO Buffers to support precise device parameter extraction.

Analog/Mixed-Signal: Full-type AC/DC/Transient simulations for modules like Op-Amps, ADC/DAC, LDO, and PLL; Verilog-A mixed simulation.

Power Electronics: Native modeling for SiC/GaN power devices, transistor-level simulation for AC-DC and DC-DC conversion topologies; scenarios including automotive, photovoltaics, and motor drives.

PDK & Modeling: Process device model extraction (IC-CAP engine), PDK verification, and standard cell library characterization.

VII. Seamless Migration

Netlist Compatibility: Supports industry-mainstream SPICE netlist formats, requiring no modifications to existing design files.

Toolchain Integration: Supports embedding into mainstream EDA design environments via standard interfaces.

Platform Support: Mainstream operating systems including Red Hat Enterprise Linux and Windows.

Progressive Replacement: Can run in parallel with existing tools for comparative validation, enabling a full switch after progressively building confidence.

VIII. Conclusion

"PanosSPICE represents Julin-tech's profound accumulation in underlying simulation algorithms," stated Jiaxin Sun, Founder of Julin-tech. "We are providing a trustworthy, high-precision 'Golden Foundation' for global semiconductor and terminal supply chain partners, helping every world-changing innovation move from the lab to mass production."

Currently, PanosSPICE has passed Tier-1 (A1 class) customer certifications in multiple mission-critical scenarios. Looking ahead, Julin-tech will continuously expand its technological boundaries, empowering the global semiconductor industry to reach new heights amidst the wave of intelligence.

IX. About PanosSPICE

PanosSPICE (formerly TJSPICE) is a True-SPICE simulation platform developed by Julin-tech, specifically engineered for IC design and IP verification scenarios requiring Golden-level device precision. As the precision infrastructure for exact transistor-level simulation, PanosSPICE covers full-process device modeling from advanced logic nodes to 3rd-generation semiconductors (SiC/GaN) and has been recognized by Tier-1 (A1 class) customers as a Signoff-grade tool.

The product has been successfully applied in critical fields such as memory, communications, and power electronics. Its fully automated IP PVT Corner verification significantly boosts verification efficiency, and its Power Integrity verification precision reaches the Golden level.

Recommended

-

Selecting SI Simulation Tools: Practical Verification of SIDesigner's 4 Core Capabilities2026.04.29

Selecting SI Simulation Tools: Practical Verification of SIDesigner's 4 Core Capabilities2026.04.29 -

How to Choose DDR5/HBM3 Signal Integrity Simulation Tools? Four Verification Standards2026.04.23

How to Choose DDR5/HBM3 Signal Integrity Simulation Tools? Four Verification Standards2026.04.23 -

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20 -

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13