复杂芯片设计中的SPICE仿真困境:精度与效率的权衡之道

-

2026.03.13

核心观点概览

· 高速接口设计面临精度与效率的两难困境

· 传统 True-SPICE 精度高但耗时数周,FastSPICE快但精度有损

· 全晶体管级物理建模是解决根本问题的技术路径——唯有器件模型足够准,系统级验证才有可信基础

一、SPICE仿真面临的核心挑战

在现代集成电路设计领域,SPICE(Simulation Program with Integrated Circuit Emphasis)仿真一直是验证电路功能和性能的核心手段。然而,随着芯片设计复杂度的指数级增长,传统SPICE仿真正面临着前所未有的挑战。

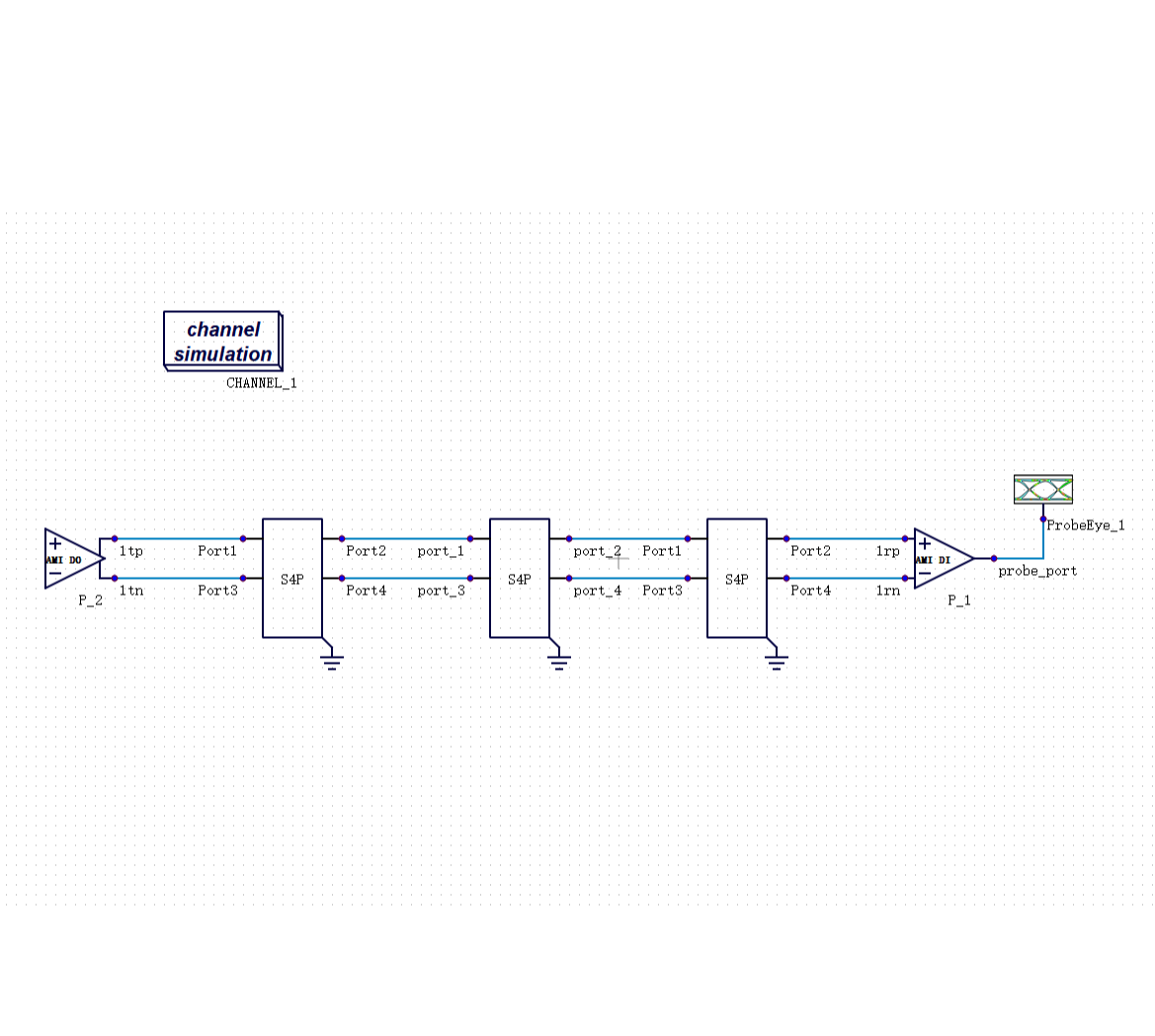

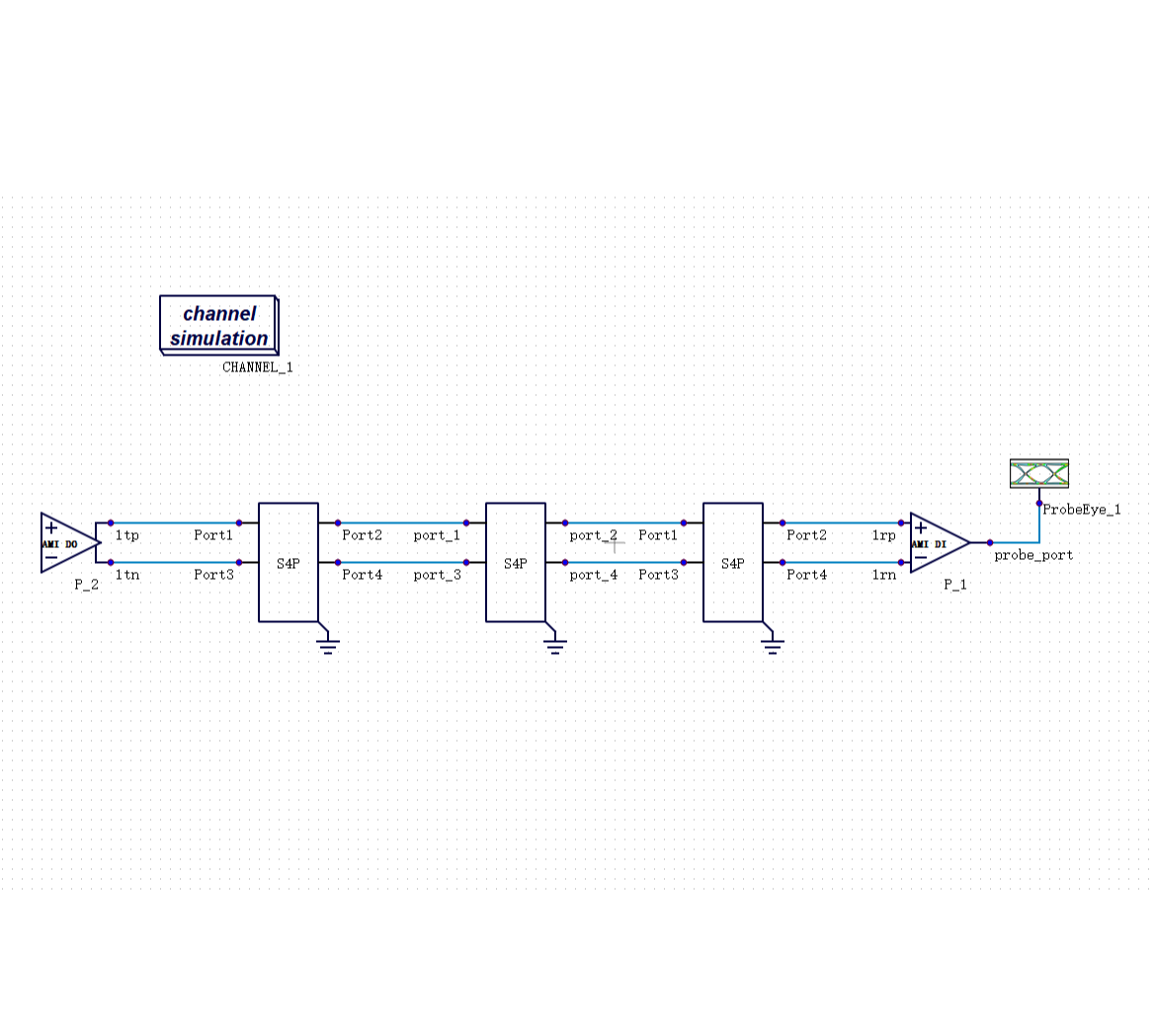

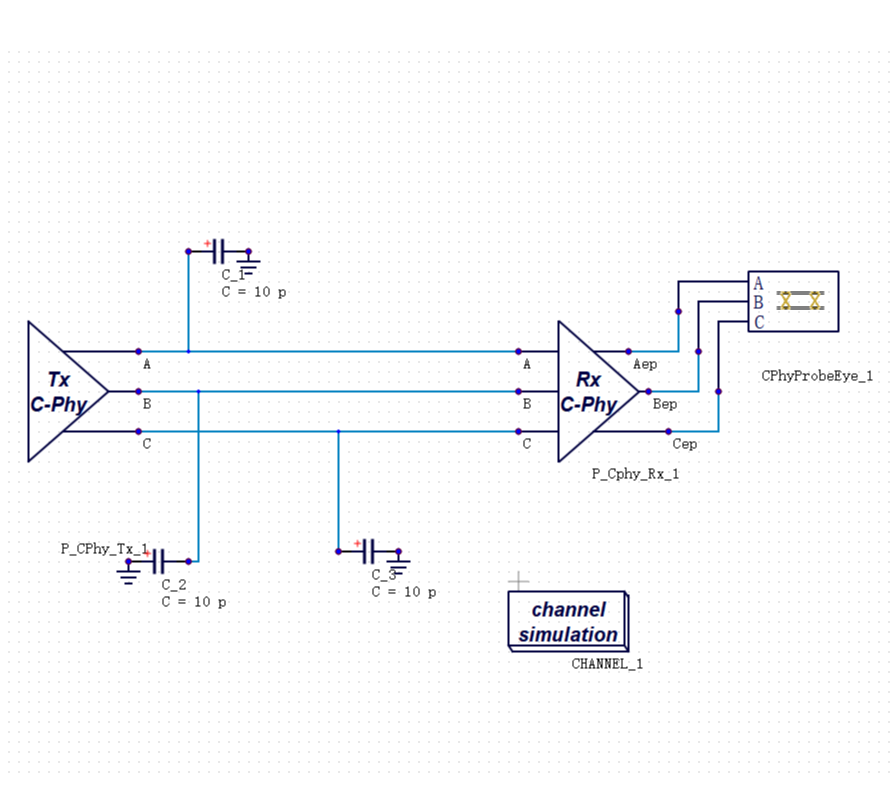

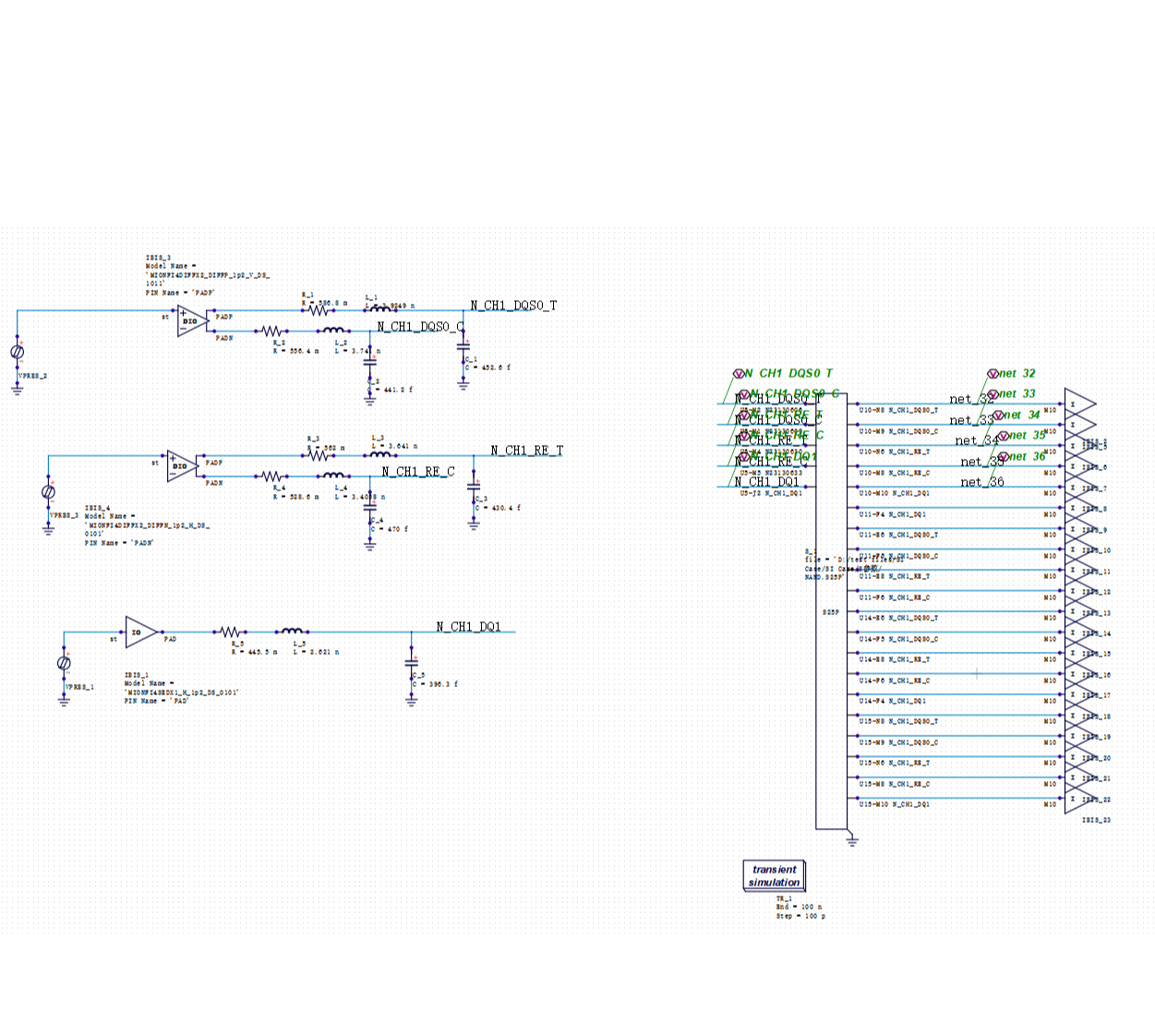

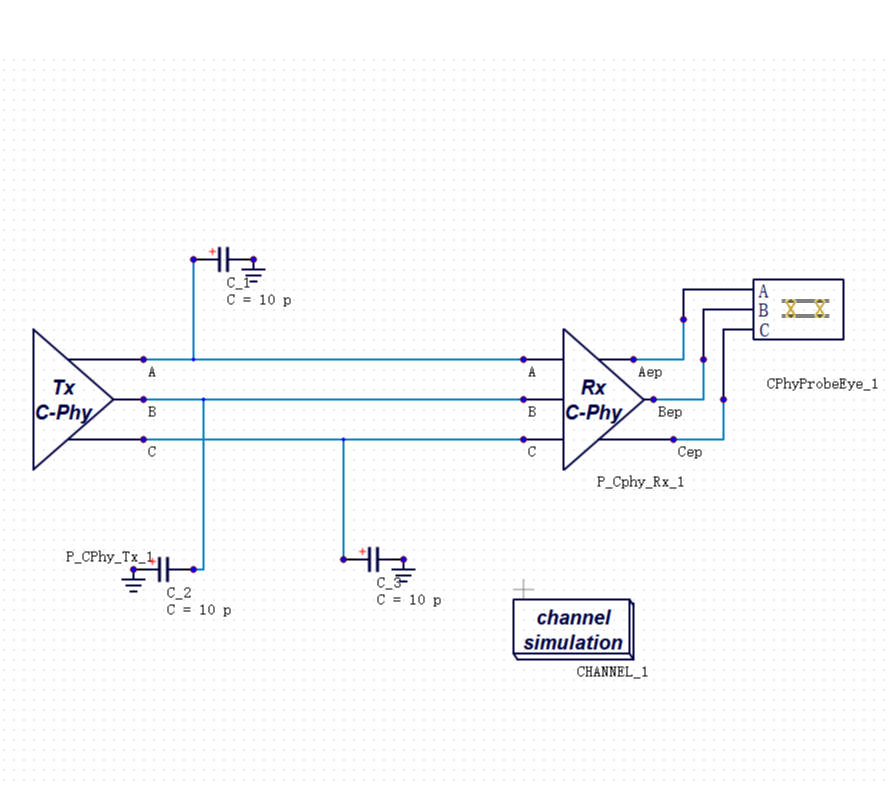

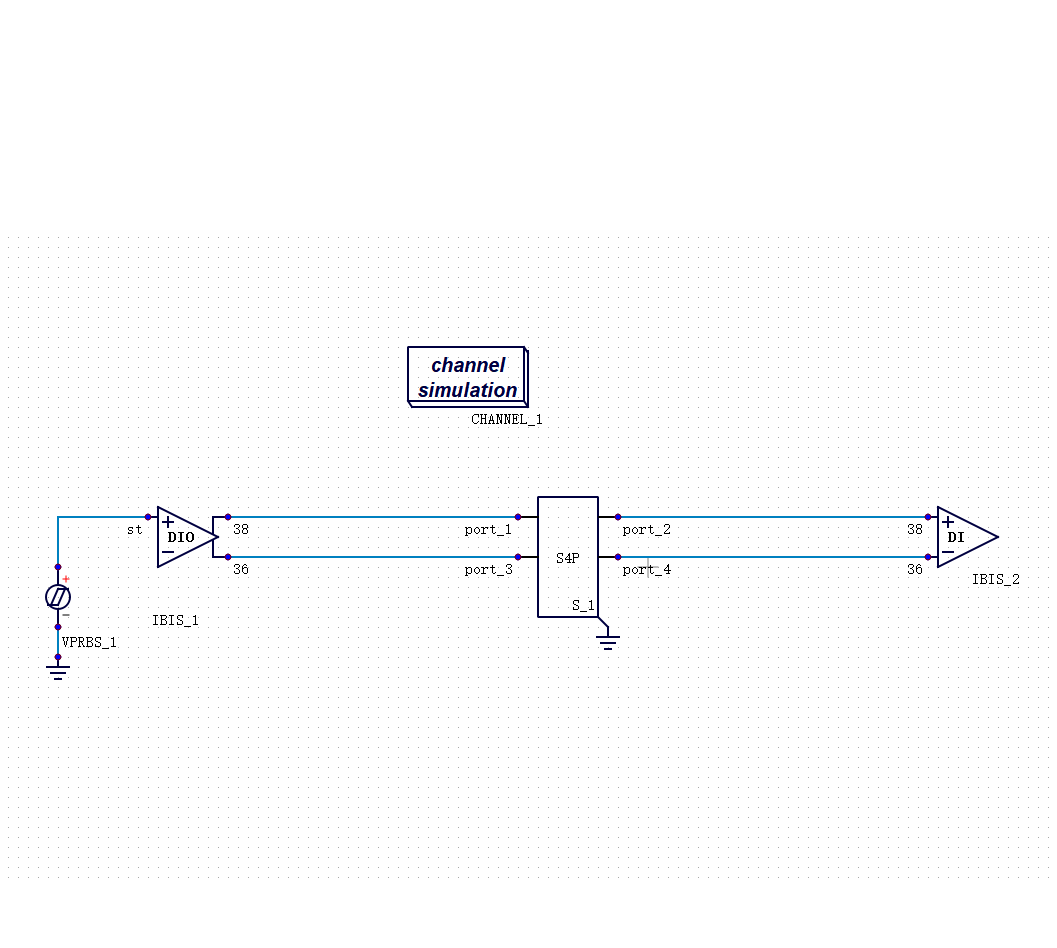

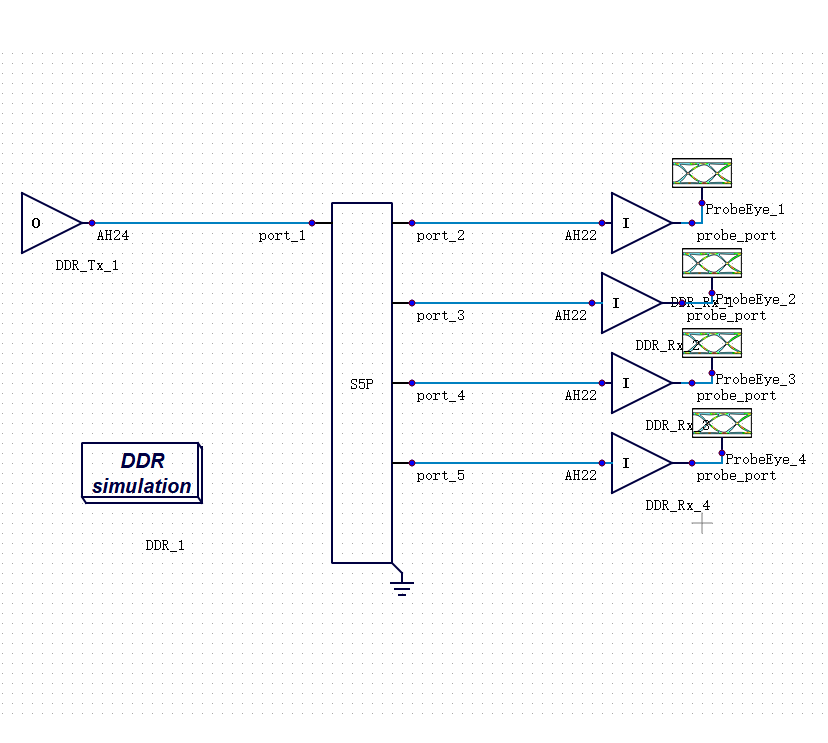

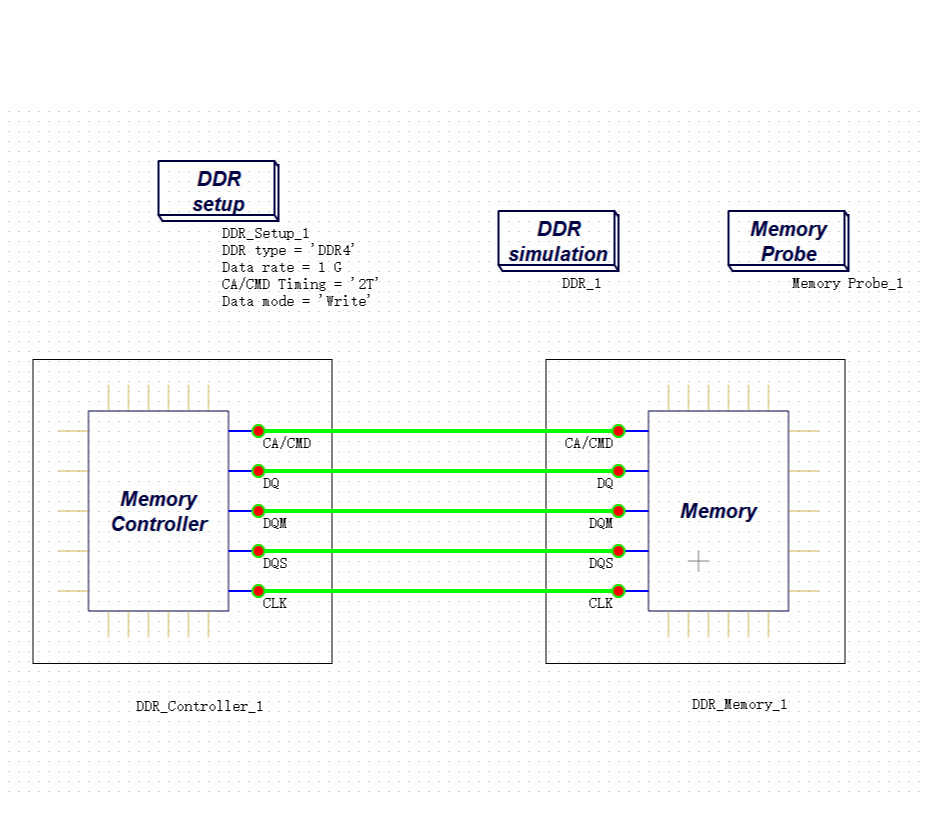

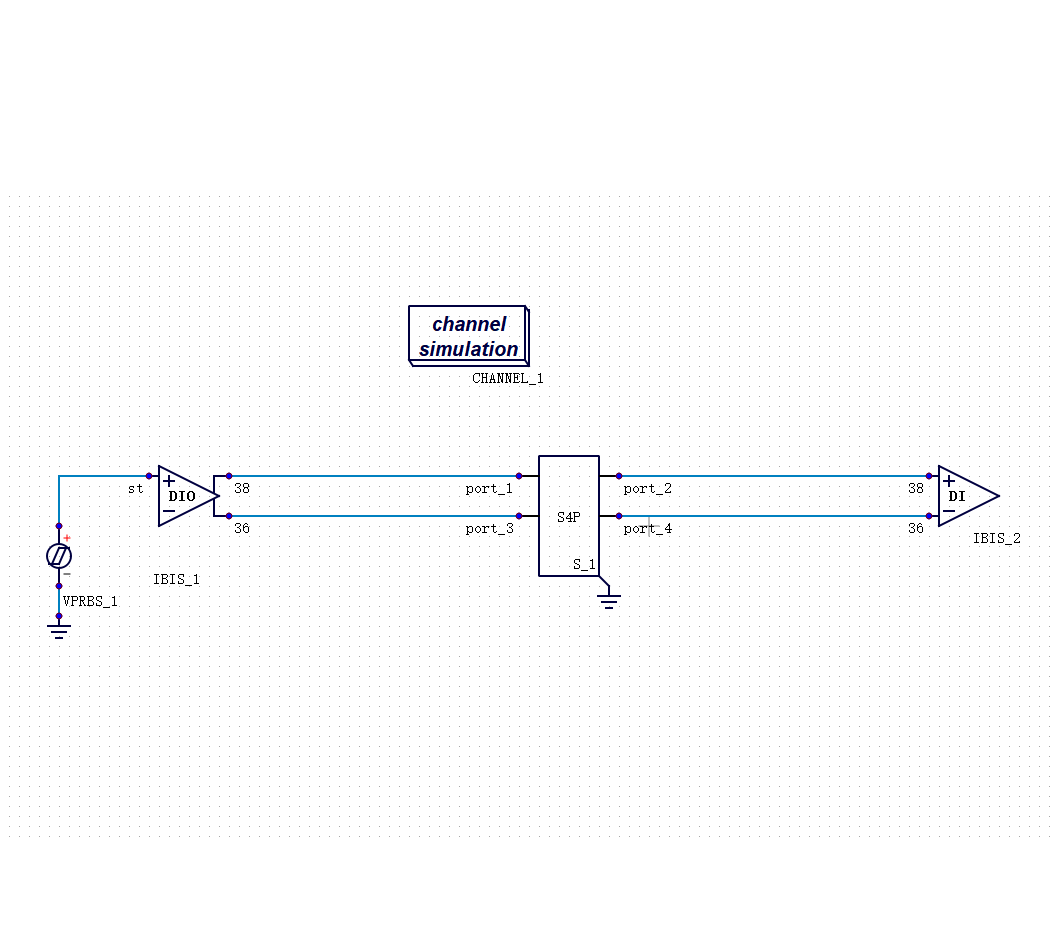

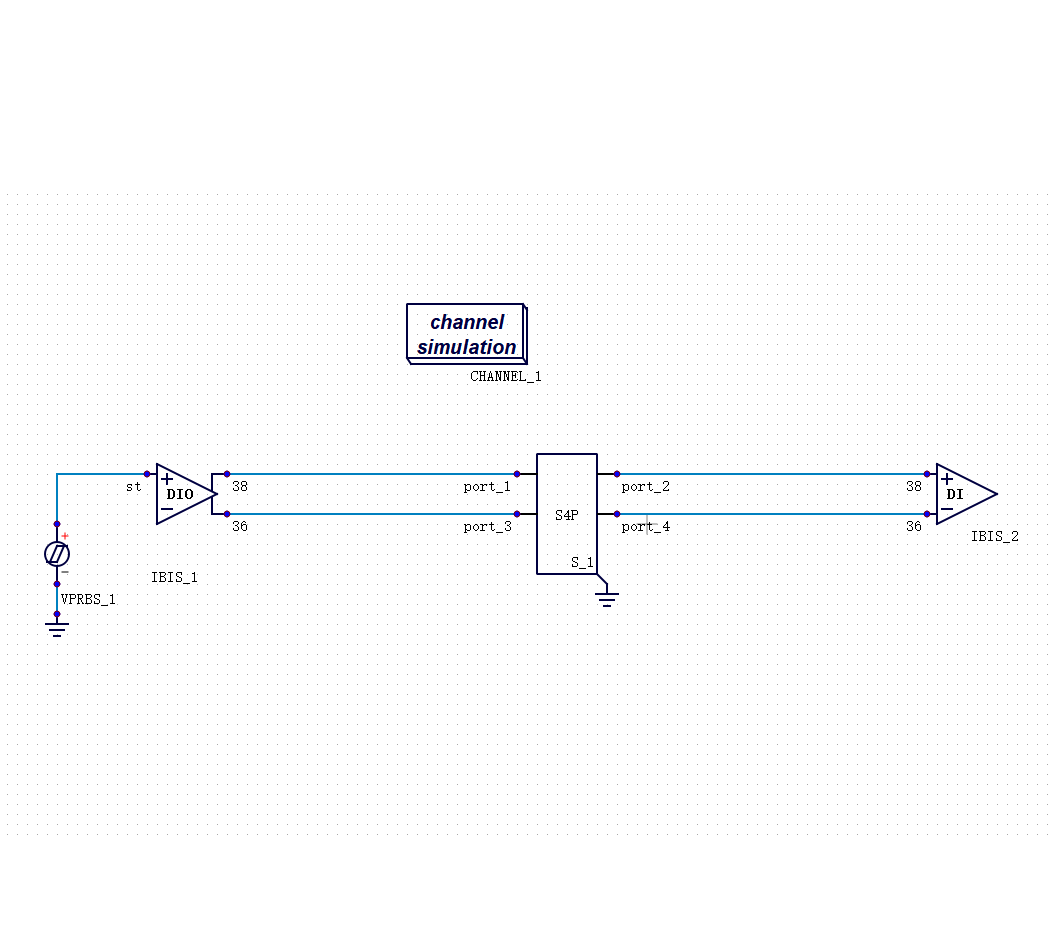

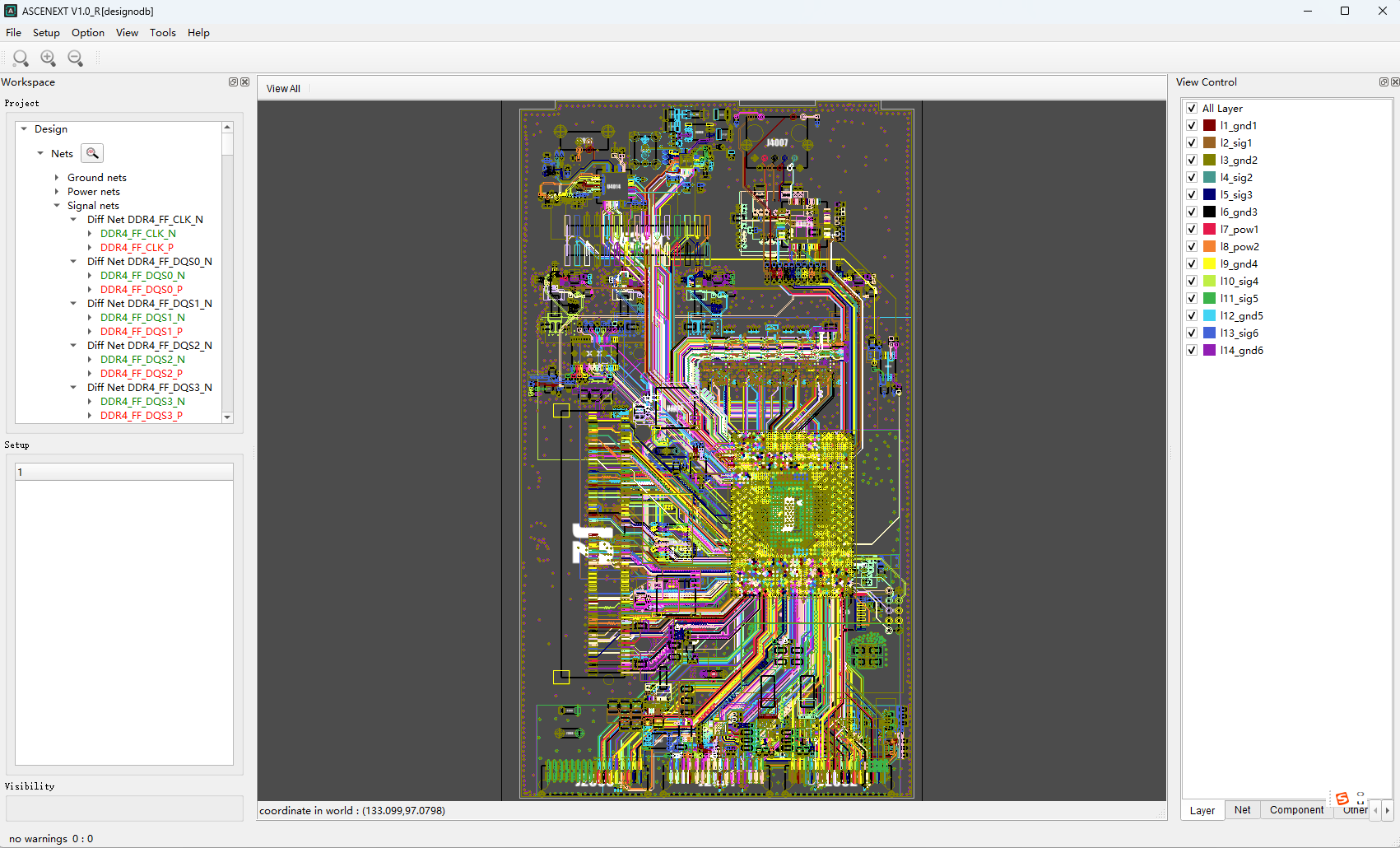

当前高速接口设计——如DDR、PCIe、UCIe等——的传输速率持续提升,信号完整性分析需要考虑的器件数量达到百万级甚至千万级。与此同时,精度要求也在极致提升:部分应用场景对误码率的要求已达到“1e-50级别”,远超传统1e-12标准。

这带来了一个行业性的两难困境:

· 采用传统True-SPICE,虽然能够保证Golden级精度,但完整的眼图分析往往需要数天甚至数周时间。对于一个典型的高速SerDes链路,完成百万次Monte-Carlo统计分析所需的计算时间,可能超过整个项目的时间窗口。

· 采用FastSPICE等加速工具,虽然能将仿真速度提升10倍以上,但精度损失可能导致在corner case下出现预测偏差。这种偏差在流片后可能演变为致命的设计缺陷。

核心矛盾:精度与效率的权衡,成为制约芯片设计效率的关键瓶颈。

二、为什么SPICE仿真越来越难?

2.1 电路规模的指数级增长

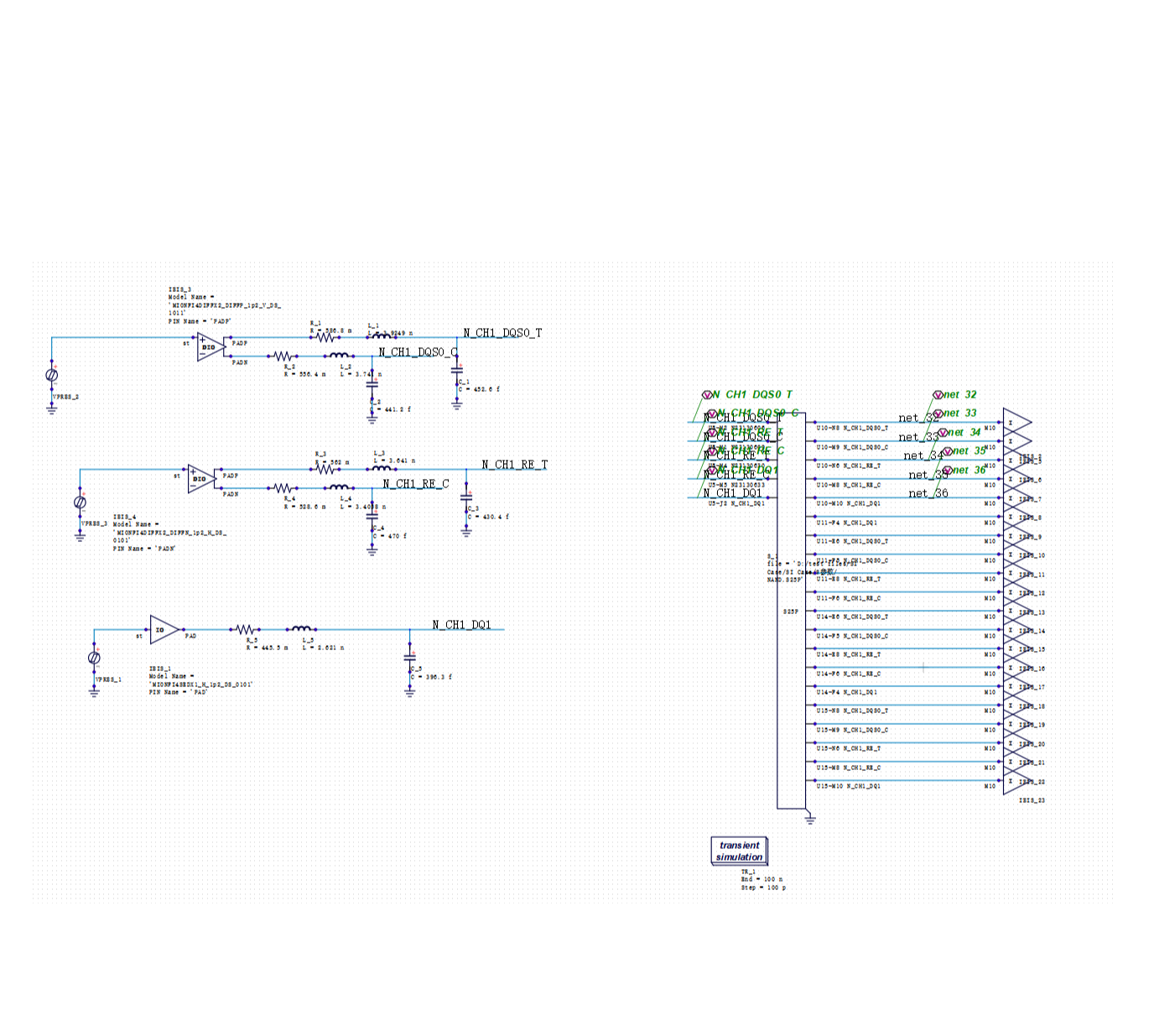

现代芯片设计中,一个高速SerDes接口的完整链路仿真,涉及的晶体管数量可达百万级;一个高速存储控制器的信号完整性分析,网络节点数更是达到千万量级。

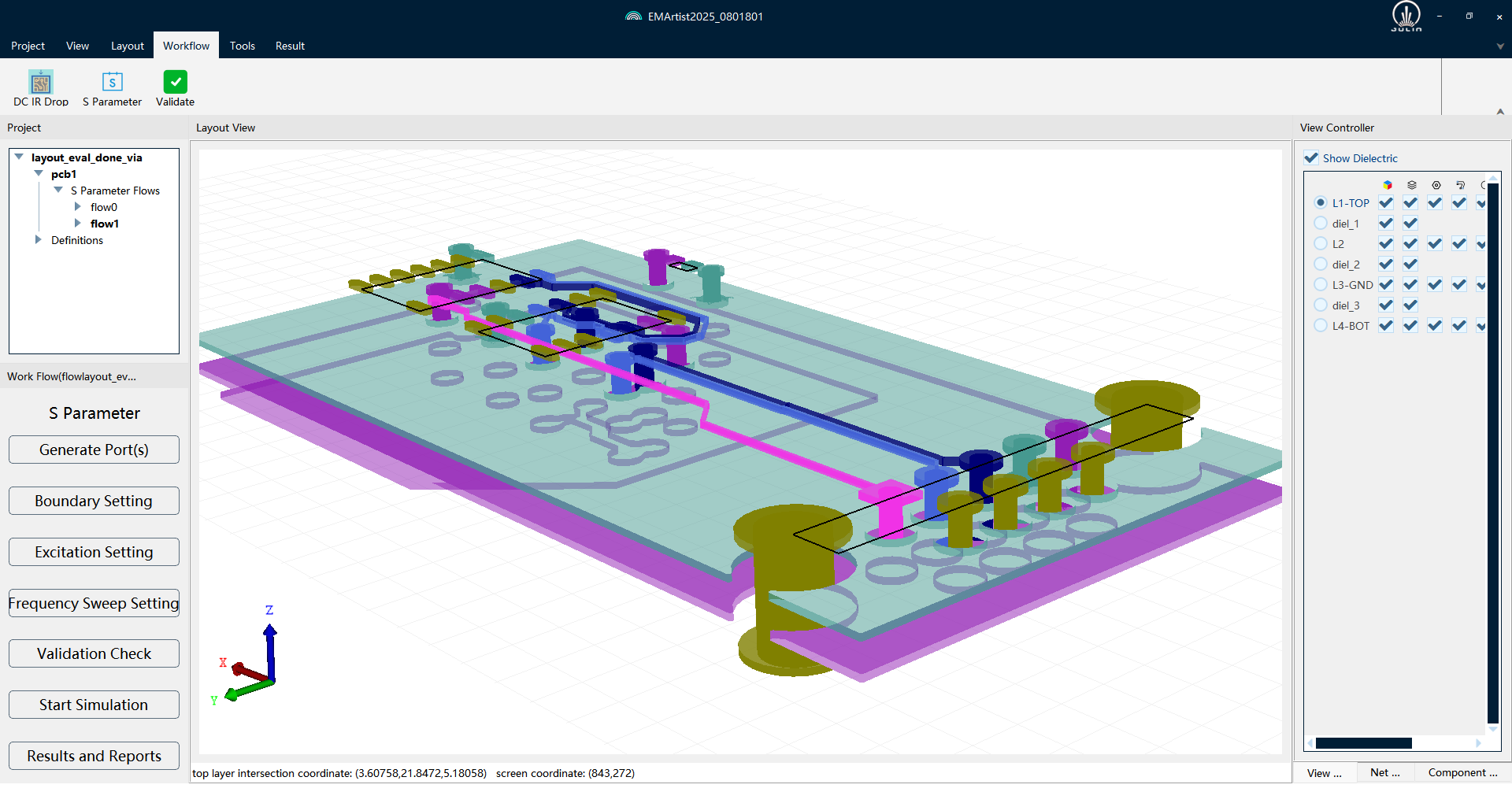

更关键的是,在高速电路中,每一条传输线的寄生参数、每一个过孔的电磁耦合、每一处阻抗不连续点,都可能对信号质量产生显著影响。SPICE需要对所有这些细节进行精确建模和求解,计算复杂度呈几何级数增长。

2.2 精度要求的极致化

误码率要求从早期标准的1e-12,到当前部分场景要求的1e-50,提升了38个数量级。

这意味着,如果采用传统的瞬态仿真方法,理论上需要模拟10^50个bit的传输过程。即使采用最先进的商业SPICE工具,完成这样的仿真在理论上也需要数年甚至数十年时间。

2.3 工艺复杂度的持续上升

从平面CMOS到FinFET,从硅基器件到第三代半导体(SiC、GaN),一个先进节点的晶体管模型可能包含上百个参数,且这些参数之间存在复杂的非线性耦合关系。

同时,芯片-封装-PCB的协同设计成为常态。信号完整性分析需要考虑整个系统级的寄生效应和电磁耦合,进一步加剧了仿真复杂度。

2.4 传统SPICE架构的固有局限

时域瞬态分析的线性成本:计算量随仿真时间线性增长。

统计分析的样本依赖:传统Monte-Carlo方法需要数以百万计的独立仿真。

精度与速度的trade-off:现有加速技术往往以牺牲部分精度为代价。

现实困境:传统方法论在新的技术需求面前,遭遇了效率瓶颈。

三、行业的技术路线分化

面对这一困境,业界形成了两种主流技术路线,但每种路线都伴随着明显的局限性。

3.1 路线A:FastSPICE——速度优先的折衷

核心思路:差异化处理——对数字电路采用简化模型,仅在关键模拟路径使用精确SPICE求解。

技术优势:显著缩短仿真时间,使大规模电路的快速迭代成为可能。

固有局限:简化模型引入额外误差源。在高速接口设计中,看似次要的数字buffer产生的开关噪声,可能通过电源网络耦合到敏感模拟电路。而简化模型可能无法捕捉这种复杂的跨域耦合效应。

行业实践:FastSPICE在早期设计迭代中表现良好,但在最终Signoff验证环节,仍需回归True-SPICE。这种"双轨制"增加了工具链复杂度。

3.2 路线B:True-SPICE——精度保证的高成本

应用领域:对可靠性要求极高的汽车电子、工业控制、航空航天等领域。

技术优势:精度有保证,可作为Signoff依据,避免因精度不足导致的流片风险。

固有局限:时间成本高昂。完成一次完整的高速接口统计眼图分析,即使在大规模服务器集群上也需要连续运行数周。每次设计变更都需要重新验证,导致大量时间浪费。

3.3 行业痛点的本质

时间成本与市场窗口的矛盾:芯片设计周期12-18个月,但高精度SPICE仿真可能占用其中30%以上的时间。

计算资源与项目预算的矛盾:大规模计算资源可能占用项目总预算的15-20%,对中小型团队是难以承受的负担。

精度保证与设计迭代的矛盾:高精度工具仿真时间长,限制了设计迭代次数。而充分迭代往往是优化设计质量的关键。

本质问题:传统技术路线无法在保证精度的前提下实现数量级的效率提升。

四、技术突破的可能方向

在看似无解的困境中,一些创新性的技术方向正在显现突破的可能性。

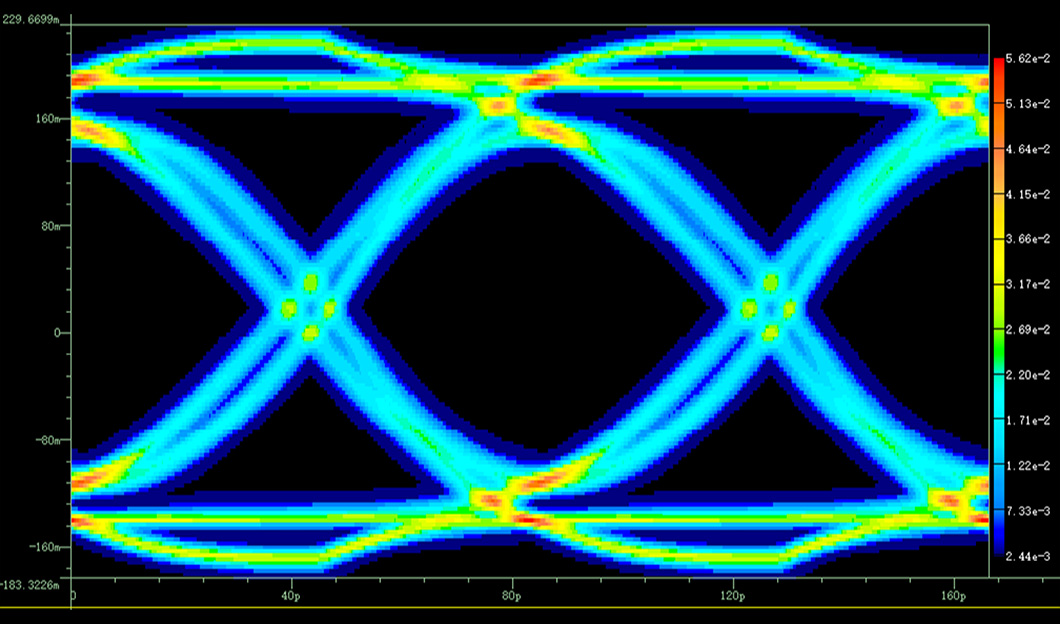

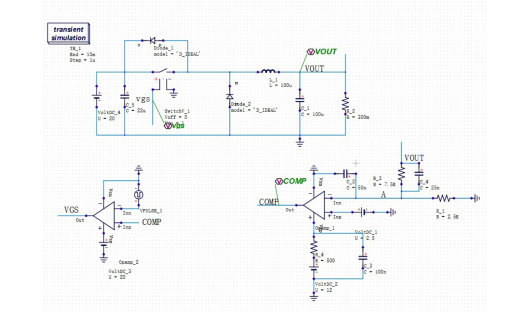

4.1 统计眼图分析技术的范式转变

传统眼图分析是"穷举式"方法——通过仿真海量bit序列来统计眼图分布。而统计眼图分析技术代表了范式转变:不再通过大量瞬态仿真来统计结果,而是通过概率分析方法直接计算眼图的统计分布。

技术原理:将信号传输建模为随机过程,综合考虑所有噪声源、抖动源及其相关性,通过数学推导直接得出眼图的概率分布函数。

效率提升机制:

· 单次分析覆盖传统方法百万次仿真的统计范围

· 分析时间从数周压缩到数小时

· 实现百万倍级的效率提升

精度表现:基于概率论框架建立分析模型,相比传统穷举式Monte-Carlo方法在精度上有所取舍,但误差可控,在多数设计迭代场景中满足工程需求。

关键突破:不是简单的加速,而是算法层面的范式转变。

4.2 其他技术方向

自适应求解策略:根据电路行为复杂度动态调整求解策略。在信号平稳区域采用大步长,在信号翻转区域使用精细步长。关键在于:在保证最终结果精度的前提下,优化中间计算过程。

并行计算架构:充分利用多核CPU和GPU,将Monte-Carlo分析、参数扫描等任务分解到数百个计算核心同时执行。结合统计方法优化,并行效率可接近线性加速比。

4.3 技术意义:重新定义精度与效率的边界

统计覆盖度显著提升:不再只能抽样验证典型corner,而是对更广泛的参数空间进行高效探索,发现传统方法难以触及的潜在问题。

设计迭代模式的改变:仿真时间从数天缩短到数小时,设计师可以进行更多轮次的优化迭代,发现传统方法难以发现的优化空间。

效率与精度的阶段性平衡:在当前技术条件下,统计眼图方法提供了一种兼顾效率与可接受精度的工程路径,降低了"双轨制"工具链的切换成本。精度与效率的深层矛盾,仍是业界持续攻克的技术方向。

结语:技术演进的新阶段

SPICE仿真技术经历了近50年的发展,从最初伯克利大学的开源项目,到如今支撑全球半导体产业的关键基础设施。但在今天,芯片设计正在经历新一轮的技术变革。

新一代SPICE技术的核心,在于算法层面的范式转变:

· 从穷举式的采样统计 → 基于数学模型的概率分析

· 从单一精度的全局求解 → 自适应的动态优化

· 从串行计算架构 → 深度并行的异构计算

这些技术探索,正在推动精度与效率边界的持续拓展。统计眼图方法代表了当前阶段的一种工程权衡——以可控的精度换取数量级的效率提升,为设计团队在时间窗口内完成更充分的迭代验证提供了可能。

然而,"在不牺牲精度的前提下实现极致效率",始终是SPICE仿真领域尚未完全解决的核心命题。随着芯片向更高性能、更低功耗、更复杂系统演进,业界对更高精度、更高效率仿真方法的需求只会持续增长。算法层面的深层突破,仍是这一领域最值得期待的技术方向。

展望未来:精度与效率的真正统一,不是一个已经到达的终点,而是一场仍在进行的技术攻坚。

技术说明:

· 本文所述统计眼图分析技术基于严格的概率论和随机过程理论

· 误差计算方法:Δ = |实测值 - 参考值| / 参考值 × 100%