PanosSPICE:确立芯片级仿真的"黄金底座"

-

2026.03.20

一、核心技术亮点

· Signoff 级器件精度,流片前最后一道真值防线:基于全物理晶体管级建模,在与业界 Golden 标准工具的系统对比验证中,电源节点电压误差达到 Golden 级,已获 A1 类头部客户认定为 Signoff 级工具。

· 全工艺覆盖,原生支持第三代半导体:从主流 CMOS(BSIM3/4、PSP)、FinFET(BSIMCMG)、SOI、Bipolar,到 SiC/GaN(与东南大学联合研发 Level 90/91 物理模型)——每一个工艺节点均实现器件级精确建模,而非行为级近似。

· IP 全自动 PVT Corner 验证,设计周期可见缩短:在 Signoff 精度下,驱动工艺角(Process)× 电压(Voltage)× 温度(Temperature)全矩阵自动化扫描,将传统人工迭代数周的验证流程压缩至数小时。

· PDK 全链路一致性,从硅片数据到签核不换精度基准:作为 IC-CAP 等建模工具的核心计算引擎,PanosSPICE 贯穿"硅片测试数据 → 器件模型提取 → PDK 验证 → 标准单元库特征化 → 客户设计验证"全流程,消除工具切换带来的精度漂移。

在集成电路迈向先进制程与异构集成的关键节点,仿真工程师面临一个无法回避的根本矛盾:True-SPICE 精度无可挑剔,但一次复杂仿真往往需要数天;FastSPICE 能提速,但精度损失可能直接导致流片风险。

PanosSPICE 的技术探索,是对这一命题在器件层的系统性回答。

二、从硅片数据到签核:精度基础设施

PanosSPICE 不是单点仿真工具,而是连接"测量数据"与"设计可信度"的精度链路。在这条链路上,同一套物理级建模基准从头贯穿到尾——这意味着任何一个环节的计算结果,都可追溯、可复现、可对齐。

三、核心技术能力

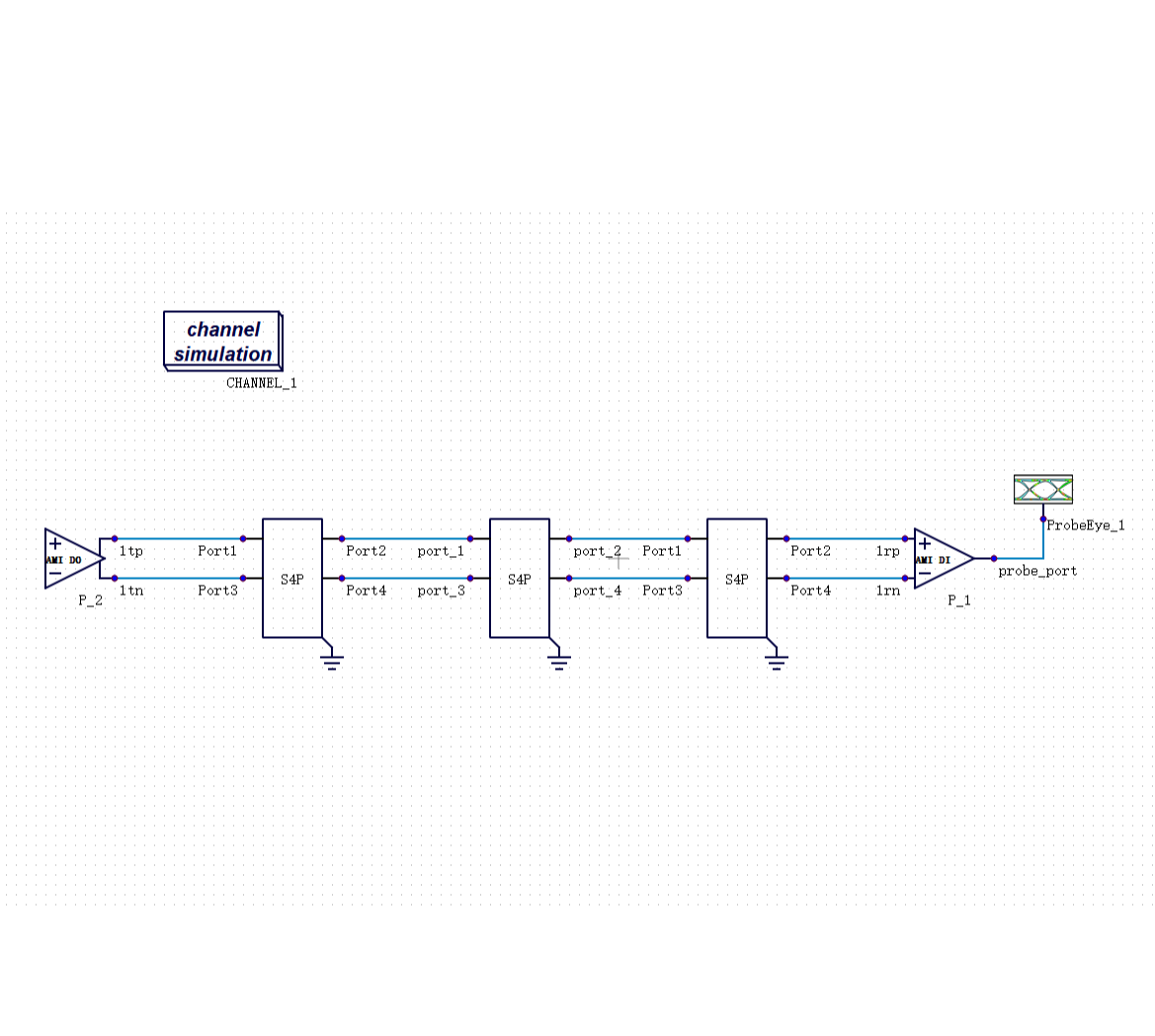

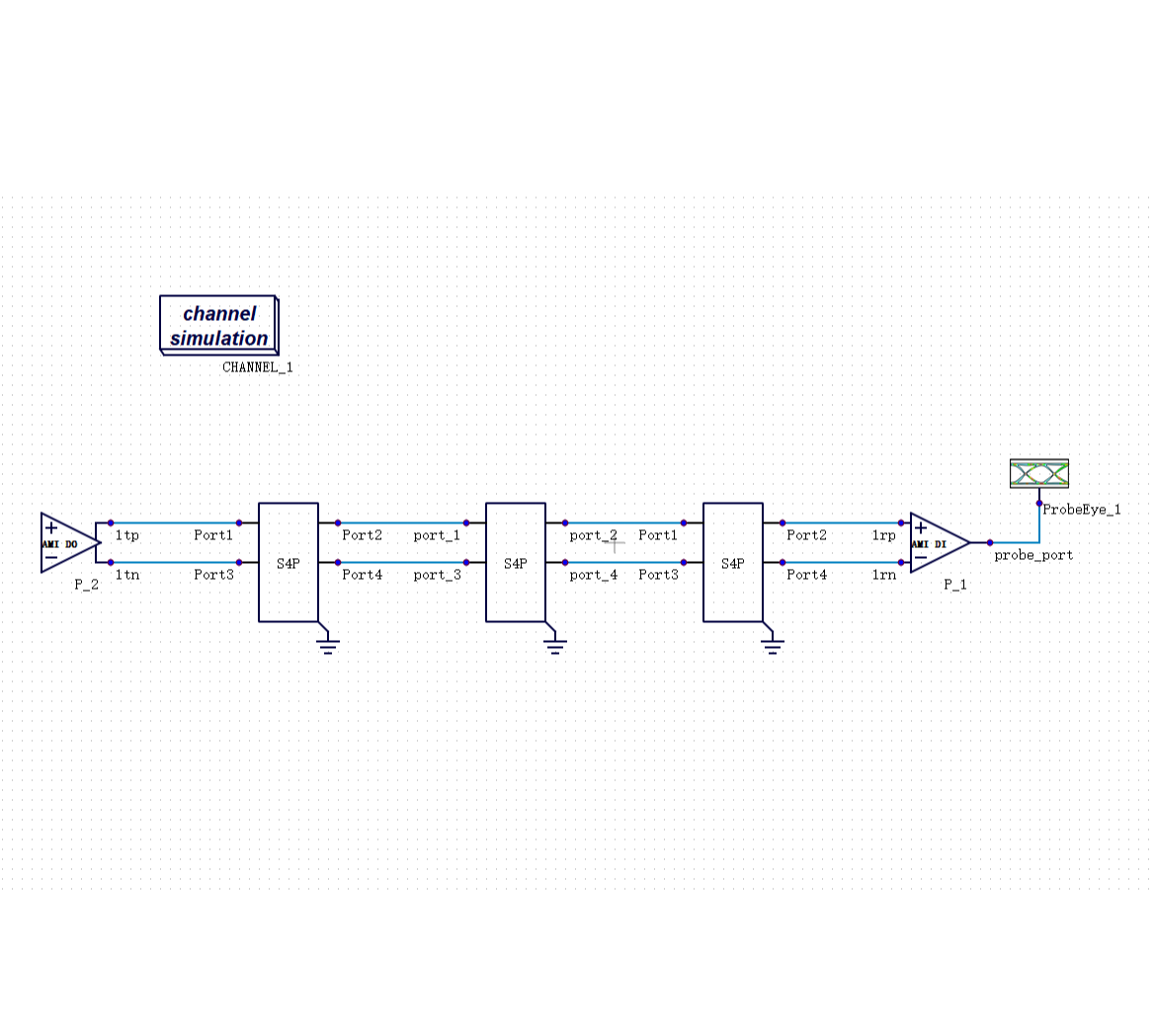

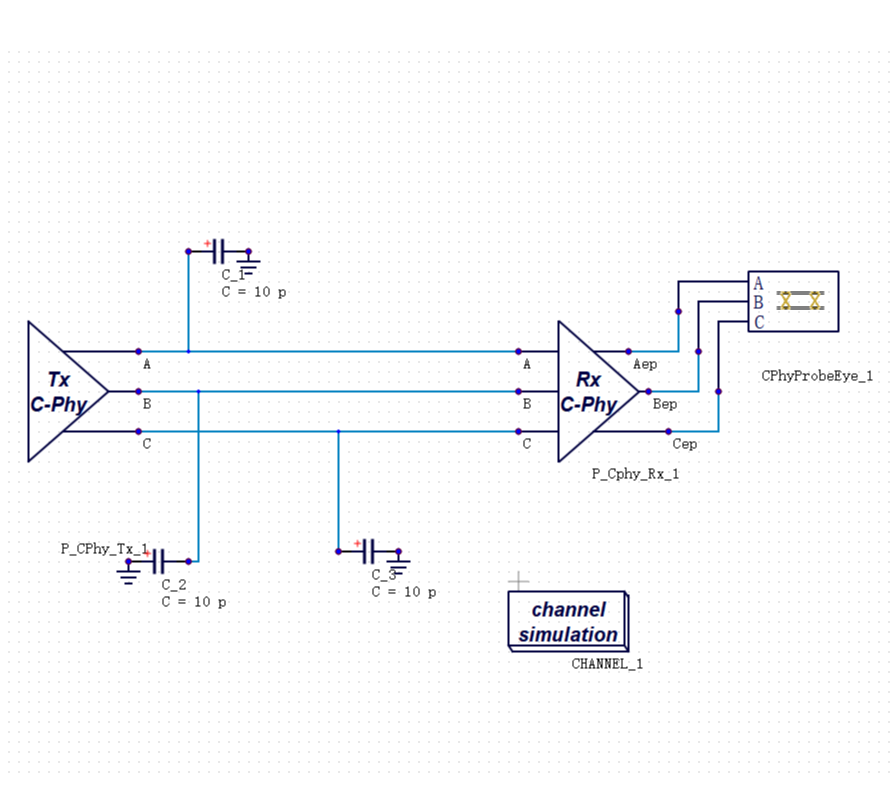

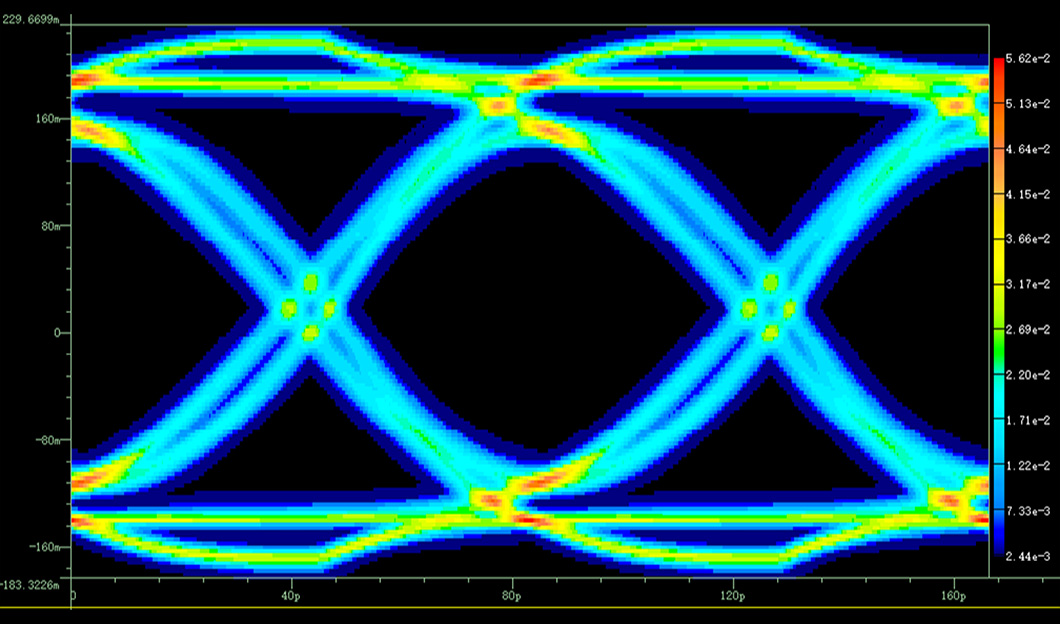

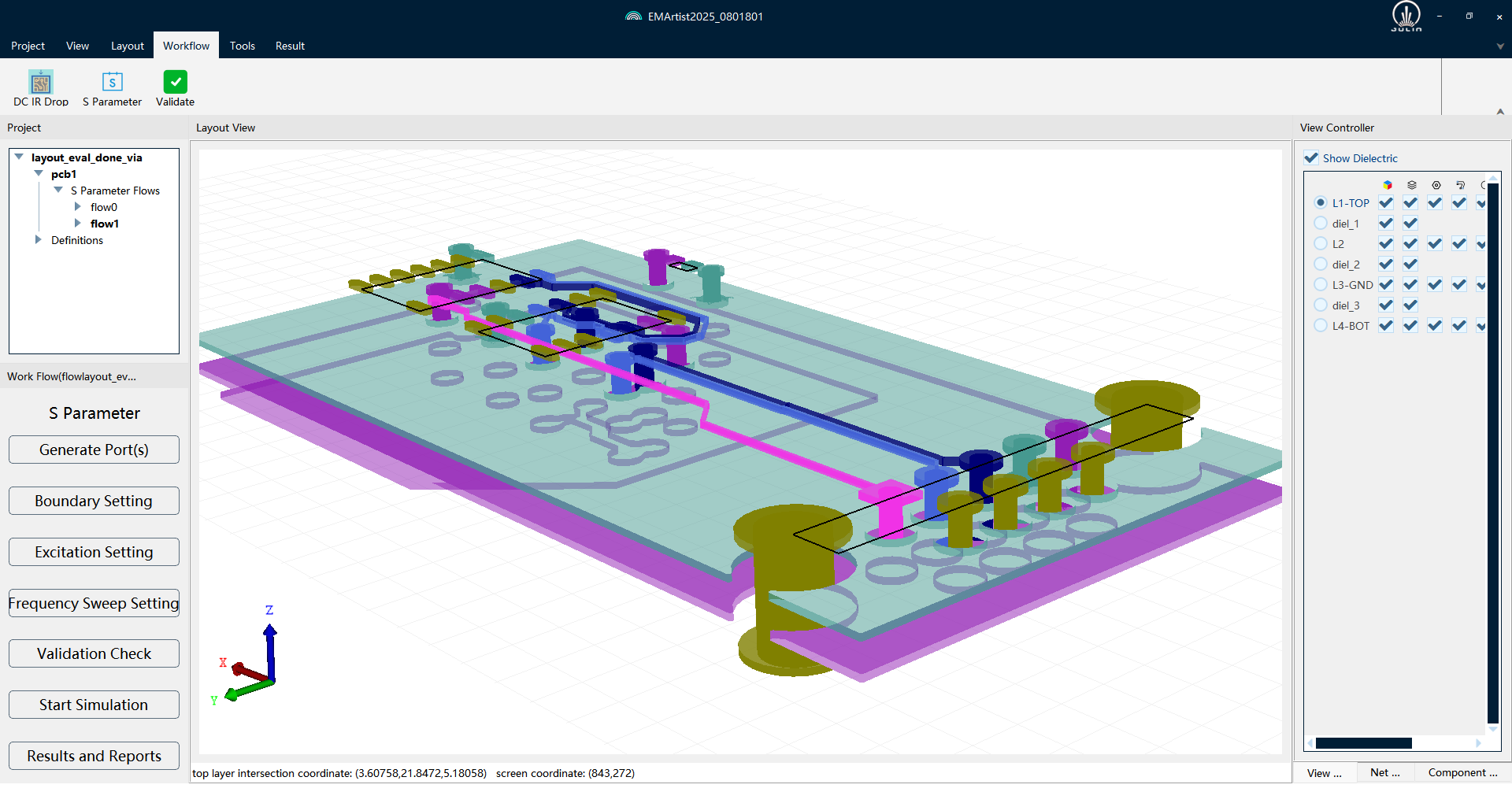

电源完整性验证:量化案例

在电源完整性(PI)分析中,PanosSPICE 展现出精度与效率的双重优势:

精确的电源网络建模:支持从芯片内部电源分配网络(PDN)到封装、PCB级别的完整建模,精确捕捉电源噪声、压降、谐振等关键特性。

实际验证案例:

IP 全自动 PVT Corner 验证:效率可见

对于 IP 开发团队,PanosSPICE 内置完整的测量(Measurement)功能与参数化扫描能力:

· 参数化扫描(Parametric Sweep):设定工艺角 × 电压 × 温度全矩阵,一键驱动全自动批量仿真,无需人工逐项配置

· Monte Carlo 统计分析:精准量化工艺偏差对 IP 关键性能指标的影响,输出良率分布

· 效率对比:传统人工迭代"跑一次改一次"——数周时间;PanosSPICE 全自动 PVT 扫描——数小时完成

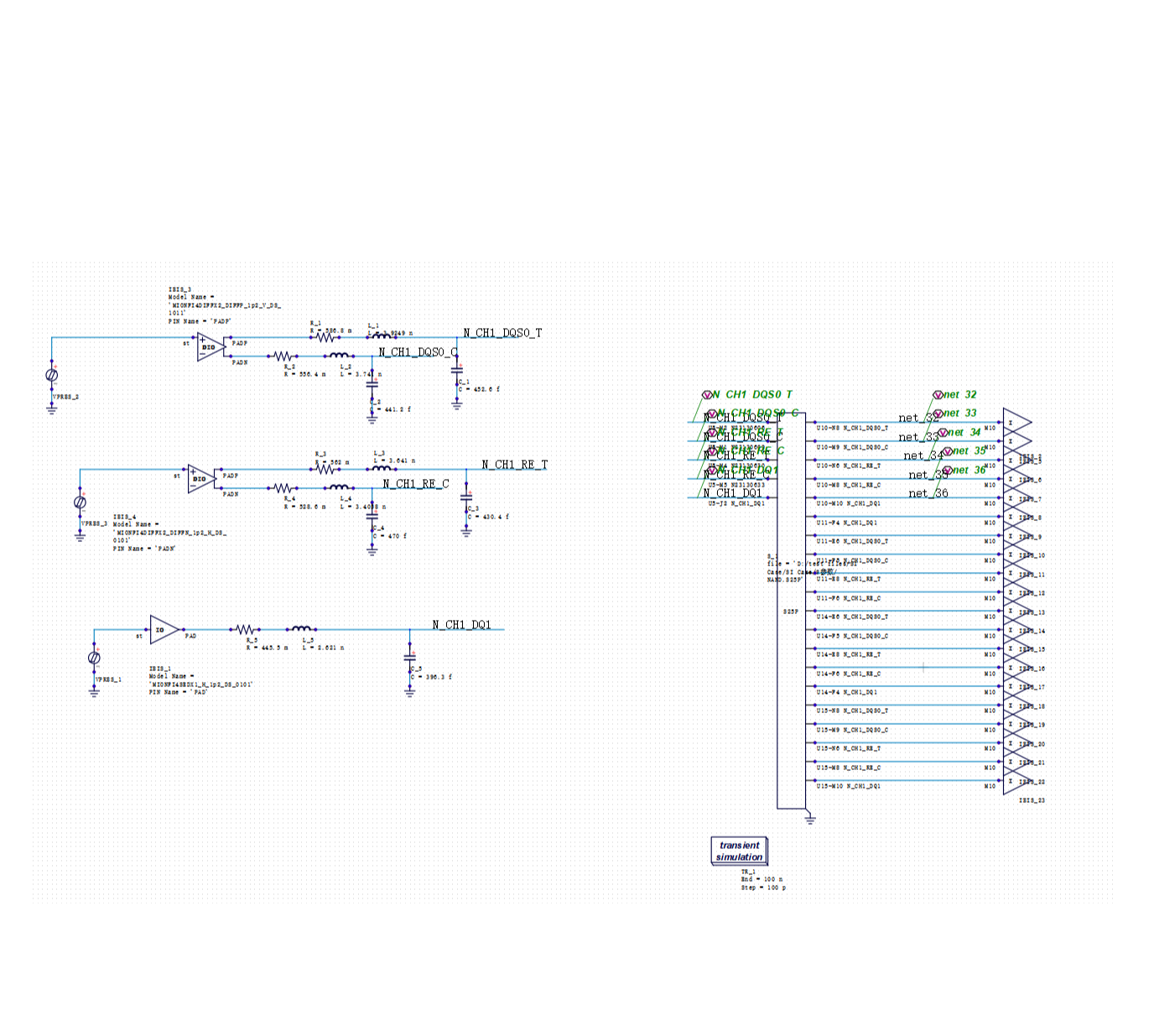

适用场景:运放、ADC/DAC、LDO、PLL、SerDes PHY、DDR PHY 等各类模拟/混合信号 IP 的跨 Corner 特性验证。

第三代半导体:原生建模,而非行为近似

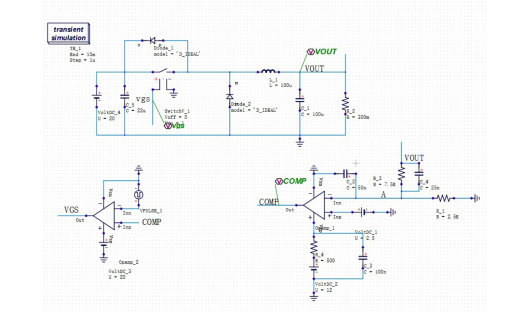

SiC(碳化硅)和 GaN(氮化镓)在新能源汽车、功率变换器、5G 射频等领域加速渗透。然而,传统 SPICE 工具对这类新材料普遍缺乏原生支持,往往依赖行为模型近似,导致高温、高压极端工况下的预测精度受限。

PanosSPICE 与东南大学联合开发的 Level 90/91 物理器件模型,实现了 SiC 和 GaN 器件的晶体管级精确建模:

· 精准捕捉开关瞬态特性(di/dt、dv/dt)

· 准确预测高温(175°C+)、高压极端工况下的器件行为

· 适用于 AC-DC、DC-DC 功率变换拓扑的晶体管级高精度仿真

差异化价值:这是目前竞争最薄弱的方向——大多数同类工具没有 SiC/GaN 原生物理模型。

Verilog-A 混合仿真

支持 Verilog-A 行为级模型与晶体管级电路在同一环境下混合仿真(支持 Verilog-AMS LRM 2.40)。复杂模拟/混合信号 IP 验证时,关键路径晶体管级精确仿真,非关键部分行为级简化——精度与效率动态平衡,无需切换工具。

四、客户评价与认证

A1 类头部客户验收结论:

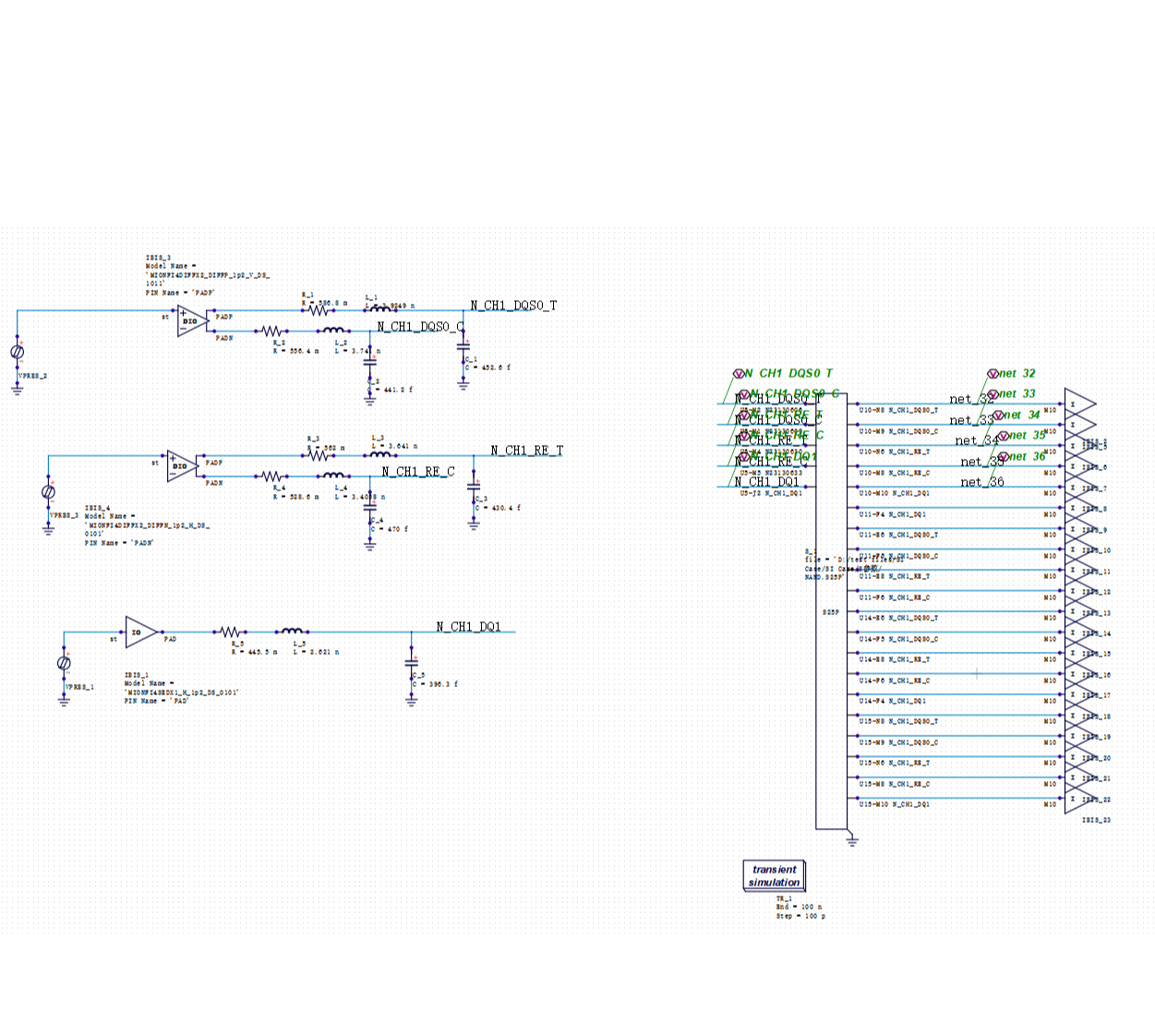

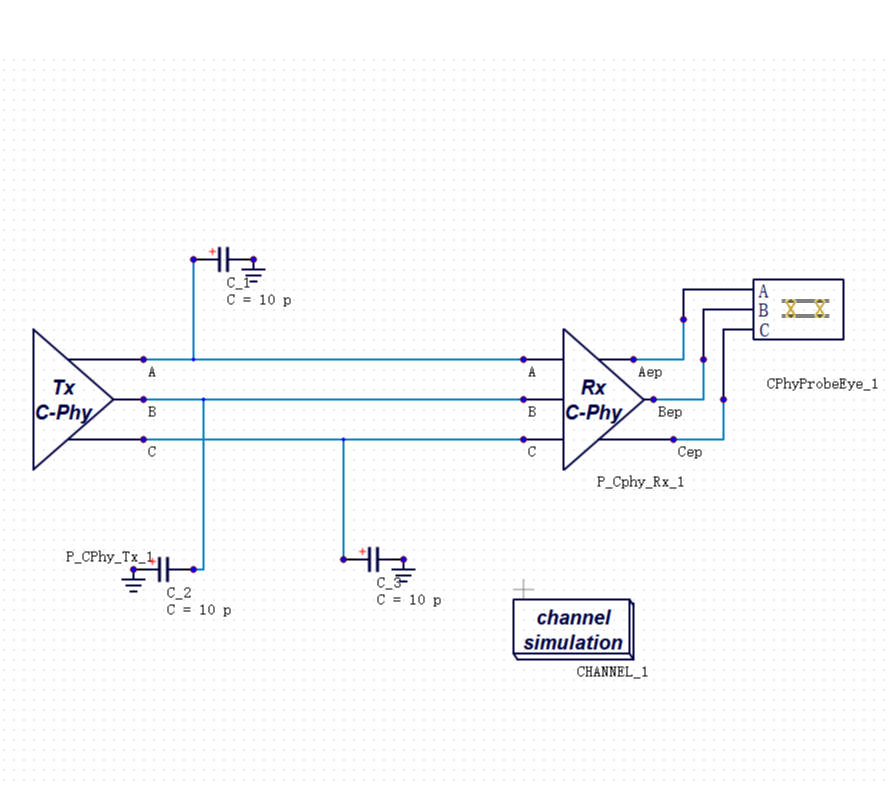

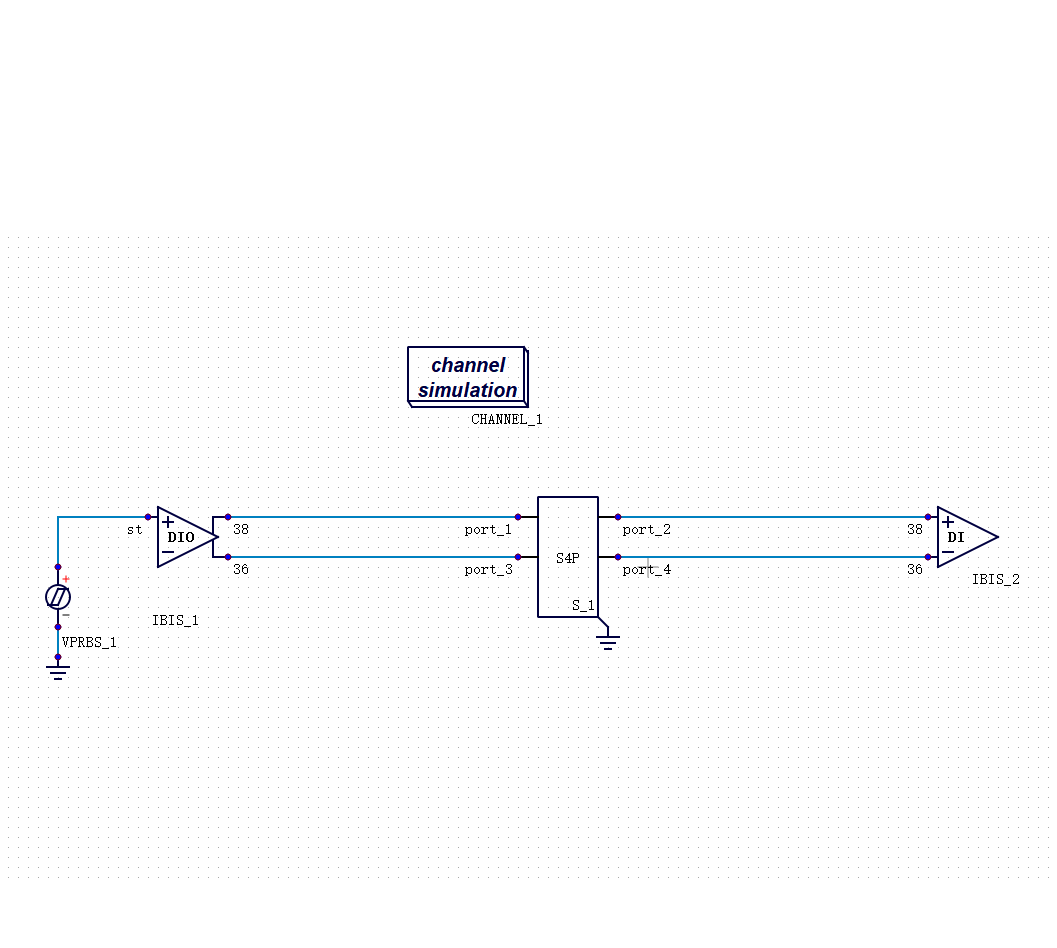

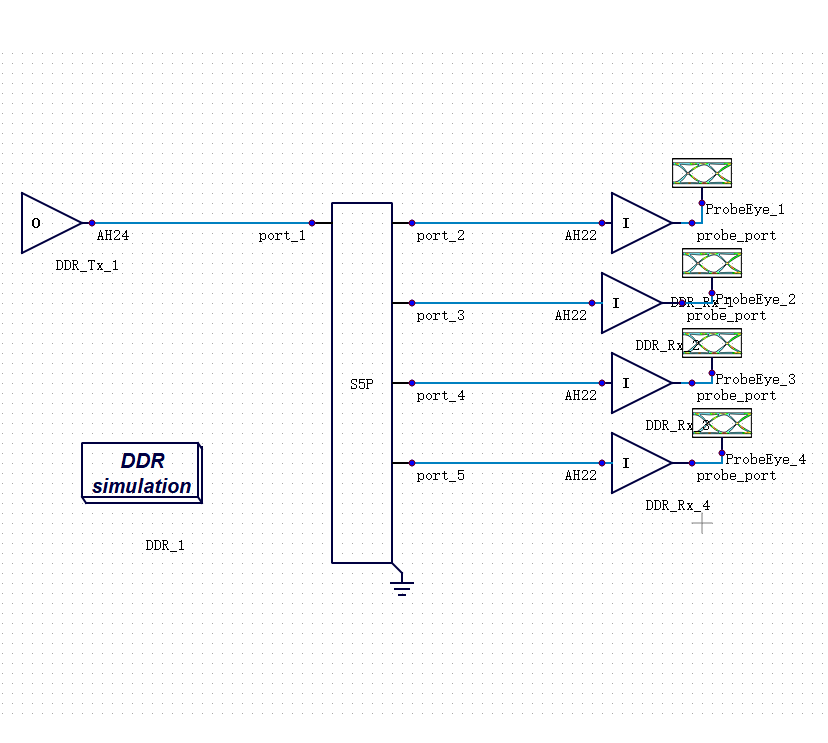

"该仿真工具在 SI/PI 分析场景下运行稳定,精度满足业界 Golden 标准要求。在多个实际项目验证中,Eye Width 误差控制在 1.2% 以内,电源节点电压误差 <5%,已达到 Signoff 级工具标准,可在实际项目中稳定应用。"

—— A1 类头部客户验收报告

工程应用价值

· 缩短设计周期:IP全自动PVT Corner验证,将人工迭代数周的验证流程压缩

· 降低流片风险:Golden级精度保证设计可靠性

· 降低工具成本:统一平台减少工具授权费用

· 提升团队效率:无需在多个工具间切换

五、技术架构:统一模型体系

PanosSPICE 采用统一 SPICE 模型架构(Unified SPICE Model),三层设计实现精度与通用性的统一:

输入层:全面兼容业界主流 SPICE 网表格式与语法规范,现有设计文件零修改接入。

仿真引擎层:9 大分析引擎,覆盖完整仿真需求——

DC/OP、AC、Transient(LSP/SI)、HPAC、HB(谐波平衡)、POP(电源完整性)、Noise、Monte-Carlo、参数化扫描

模型支持层:

· 主流 CMOS:BSIM3/4、PSP

· FinFET:BSIMCMG;SOI、Bipolar(VBIC 等)

· 第三代半导体:SiC/GaN Level 90/91(联合东南大学)

· 覆盖从 28nm 到先进制程全工艺节点

六、应用场景

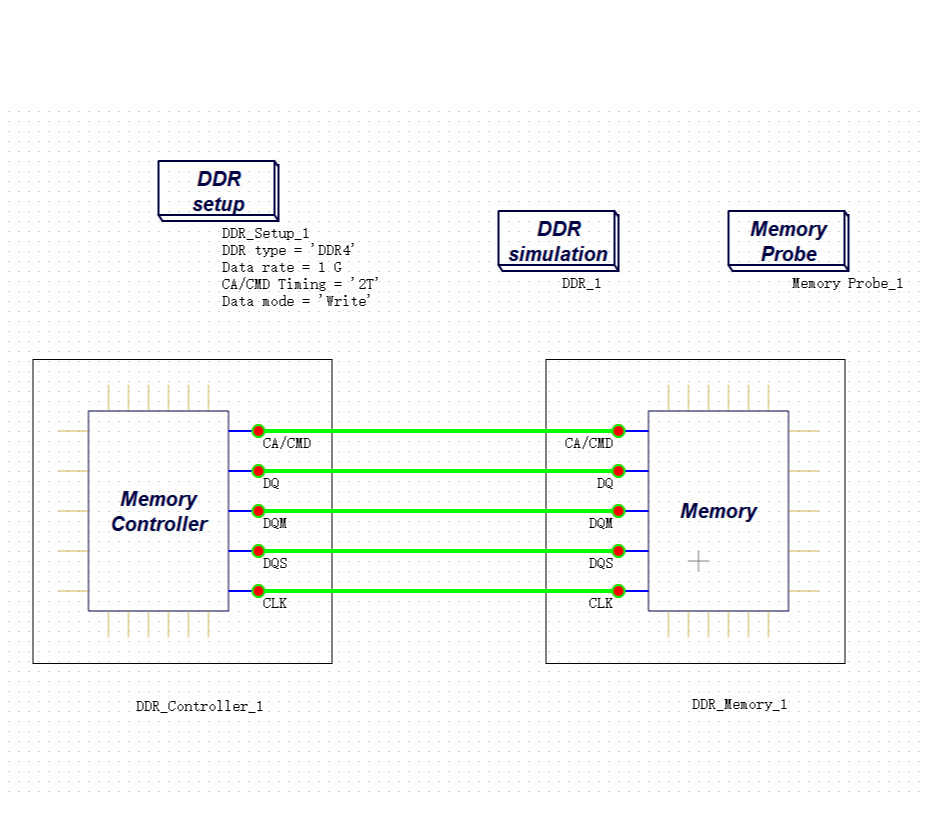

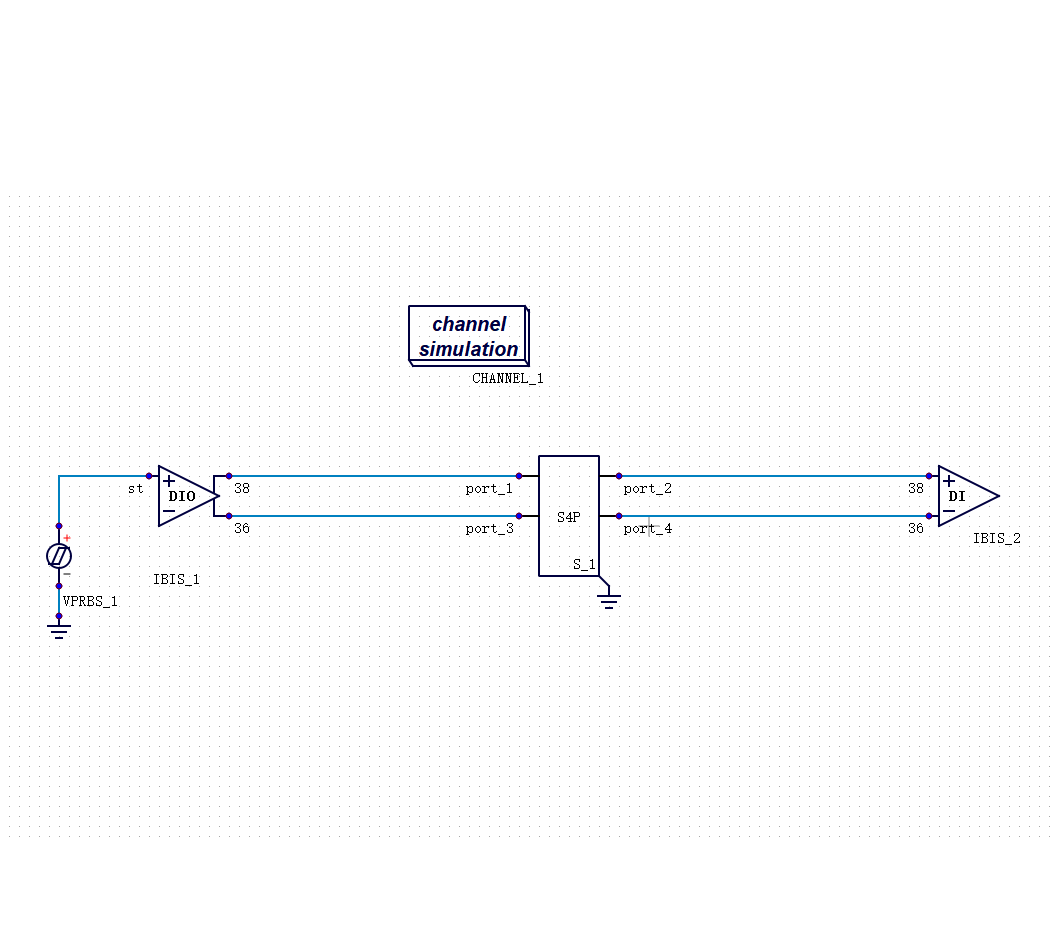

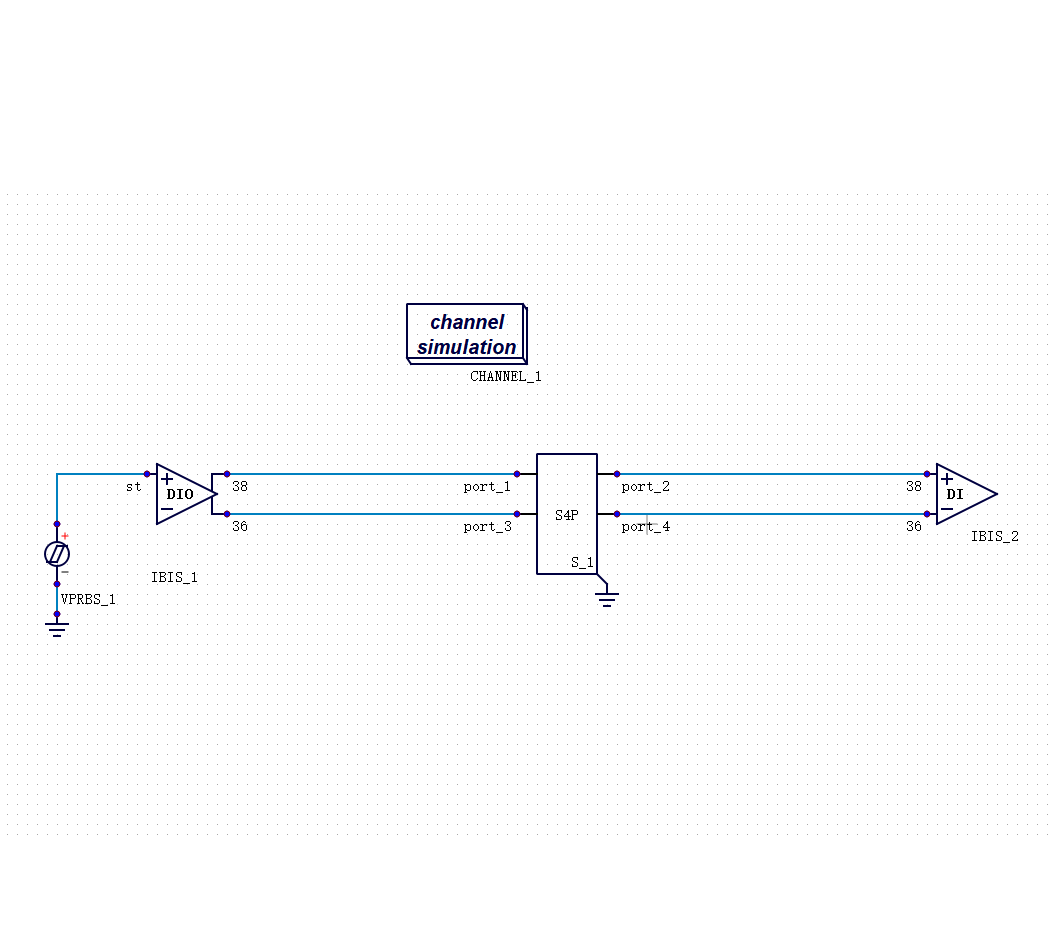

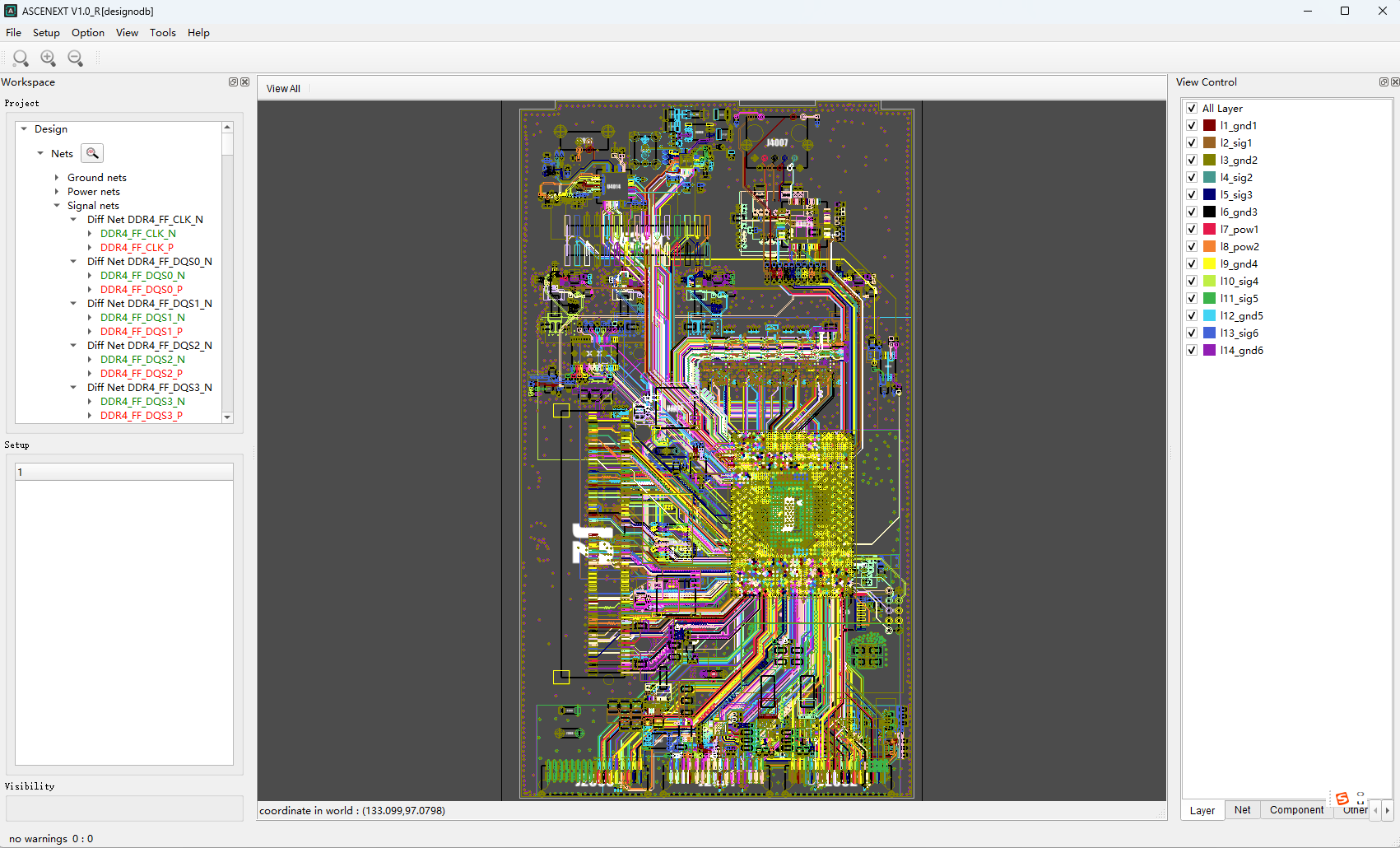

高速数字:DDR5/6、PCIe、SerDes 等高速接口 PHY 电路全 PVT Corner 验证;IO Buffer 晶体管级建模,支撑精确器件参数提取

模拟 / 混合信号:运放、ADC/DAC、LDO、PLL 等模块 AC/DC/Transient 全类型仿真,Verilog-A 混合仿真

功率电子:SiC/GaN 功率器件原生建模,AC-DC、DC-DC 变换拓扑晶体管级仿真;车载、光伏、电机驱动场景

PDK 与建模:工艺器件模型提取(IC-CAP 引擎)、PDK 验证、标准单元库特征化

七、无感迁移

· 网表兼容:支持业界主流 SPICE 网表格式,无需修改现有设计文件

· 工具链集成:支持通过标准接口嵌入主流 EDA 设计环境

· 平台支持:Redhat Enterprise Linux 及 Windows 主流操作系统

· 渐进式替换:可与现有工具并行对比验证,逐步建立信心后全面切换

八、结语

"PanosSPICE 代表了巨霖在底层仿真算法上的厚积薄发。"巨霖科技创始人孙家鑫表示:"我们正在为全球半导体及终端产业链伙伴提供一个可信赖、高精度的'黄金底座',助力每一项改变世界的创新从实验室走向量产。"

目前,PanosSPICE 已在多个关键任务场景中通过 A1 类客户认证。未来,巨霖科技将持续拓展技术边界,助力全球半导体产业在智能化浪潮中不断攀升。

九、关于 PanosSPICE

PanosSPICE(原 TJSPICE)是巨霖科技开发的 True-SPICE 仿真平台,专为需要 Golden 级器件精度的芯片设计与 IP 验证场景而生。作为晶体管级精确仿真的精度基础设施,PanosSPICE 覆盖从先进逻辑制程到第三代半导体(SiC/GaN)的全制程器件建模,已被头部 A1 类客户认定为 Signoff 级工具。

产品已成功应用于存储、通信、功率电子等多个关键领域,IP 全自动 PVT Corner 验证大幅提升验证效率,电源完整性验证精度达 Golden 级。