-

2026.01.26巨霖科技首届 SI/PI 高阶技术研讨会成功举办查看更多

2026.01.26巨霖科技首届 SI/PI 高阶技术研讨会成功举办查看更多 -

2026.01.19全文转载 | 多行业以数学“求解”产业卡脖子难题查看更多

2026.01.19全文转载 | 多行业以数学“求解”产业卡脖子难题查看更多 -

2026.01.05ICCM 2025|巨霖科技孙家鑫:数学是通往“所仿即所得”的唯一精确语言查看更多

2026.01.05ICCM 2025|巨霖科技孙家鑫:数学是通往“所仿即所得”的唯一精确语言查看更多 -

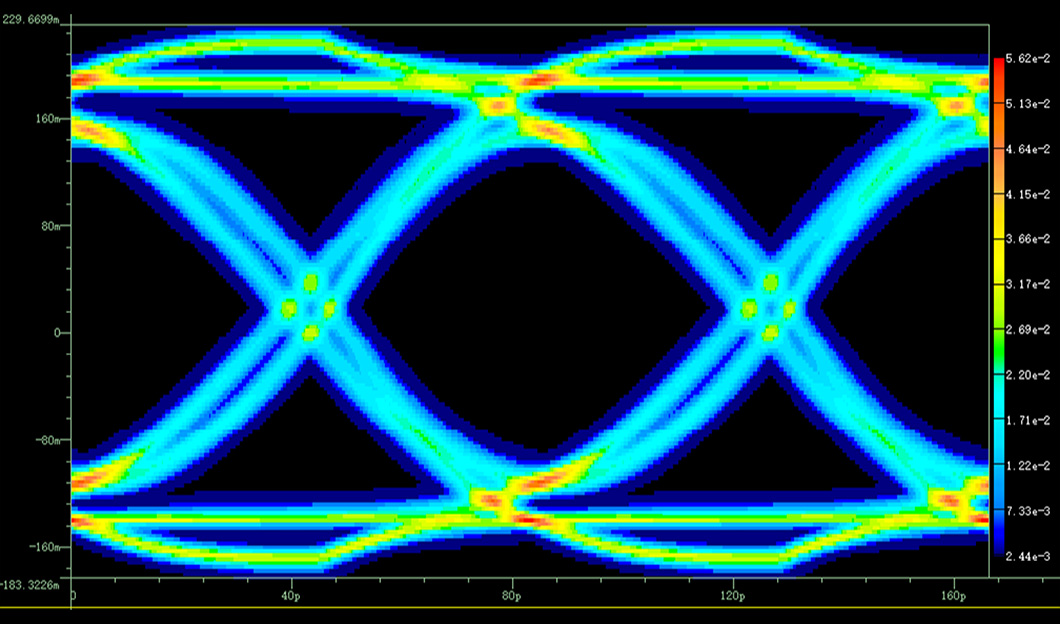

2025.12.08ICCAD 2025 | 国产SI仿真工具的破局之道

2025.12.08ICCAD 2025 | 国产SI仿真工具的破局之道ICCAD 2025 | 国产SI仿真工具的破局之道

查看更多 -

2025.12.01EEWORLD | 巨霖科技孙家鑫:EDA行业只有第一没有第二查看更多

2025.12.01EEWORLD | 巨霖科技孙家鑫:EDA行业只有第一没有第二查看更多 -

2025.12.01巨霖创始人孙家鑫:以Golden级精度SI/PI签核平台SIDesigner,赋能高保真系统设计查看更多

2025.12.01巨霖创始人孙家鑫:以Golden级精度SI/PI签核平台SIDesigner,赋能高保真系统设计查看更多 -

2025.10.16喜讯!巨霖科技荣获“湾芯奖-技术创新奖”

2025.10.16喜讯!巨霖科技荣获“湾芯奖-技术创新奖”巨霖科技(上海)有限公司凭借业界领先的EDA方案,从众多参评企业中脱颖而出,荣膺“湾芯奖-技术创新奖”。

查看更多 -

2025.09.26喜讯!巨霖科技荣获安永复旦“2025最具潜力企业”

2025.09.26喜讯!巨霖科技荣获安永复旦“2025最具潜力企业”9月26日,安永复旦“2025最具潜力企业”评选结果在上海揭晓,巨霖荣获“最具潜力企业奖”。

查看更多 -

2025.07.24巨霖科技孙家鑫的经营之道

2025.07.24巨霖科技孙家鑫的经营之道近日,我司创始人兼董事长孙家鑫先生接受半导体行业观察媒体的采访。(全文转载自半导体芯闻)

查看更多 -

2025.07.23巨霖科技仿真突围战:以技术信仰攻克EDA高地

2025.07.23巨霖科技仿真突围战:以技术信仰攻克EDA高地近日,我司创始人兼董事长孙家鑫先生接受电子创新网媒体的采访。(全文转载自电子创新网张国斌)

查看更多

探索更多

-

巨霖科技首届 SI/PI 高阶技术研讨会成功举办2026.01.26

巨霖科技首届 SI/PI 高阶技术研讨会成功举办2026.01.26 -

全文转载 | 多行业以数学“求解”产业卡脖子难题2026.01.19

全文转载 | 多行业以数学“求解”产业卡脖子难题2026.01.19 -

ICCM 2025|巨霖科技孙家鑫:数学是通往“所仿即所得”的唯一精确语言2026.01.05

ICCM 2025|巨霖科技孙家鑫:数学是通往“所仿即所得”的唯一精确语言2026.01.05 -

ICCAD 2025 | 国产SI仿真工具的破局之道2025.12.08

ICCAD 2025 | 国产SI仿真工具的破局之道2025.12.08 -

EEWORLD | 巨霖科技孙家鑫:EDA行业只有第一没有第二2025.12.01

EEWORLD | 巨霖科技孙家鑫:EDA行业只有第一没有第二2025.12.01 -

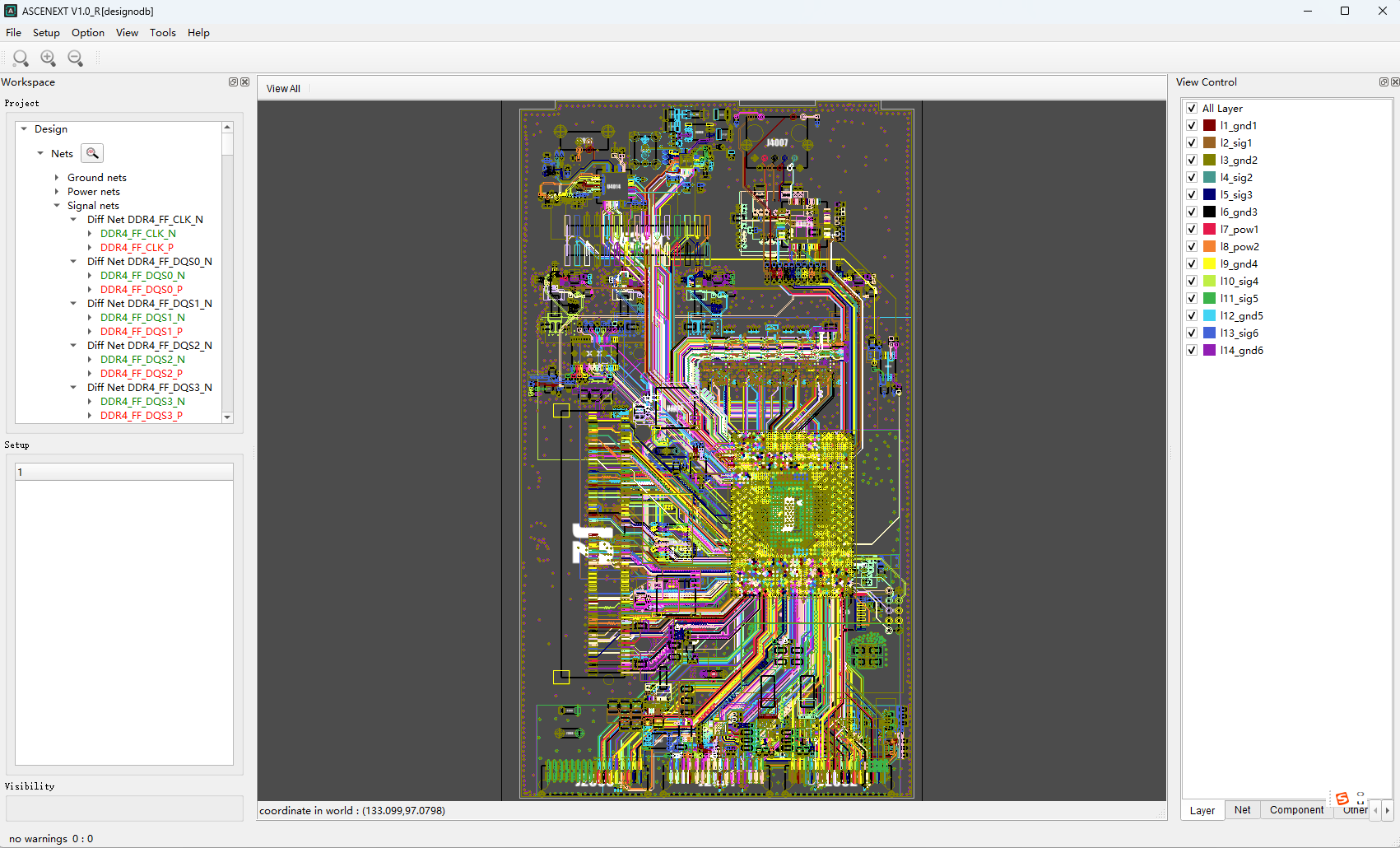

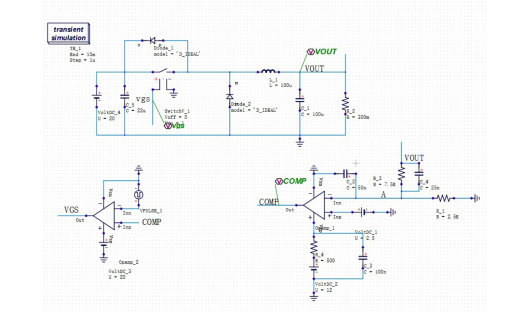

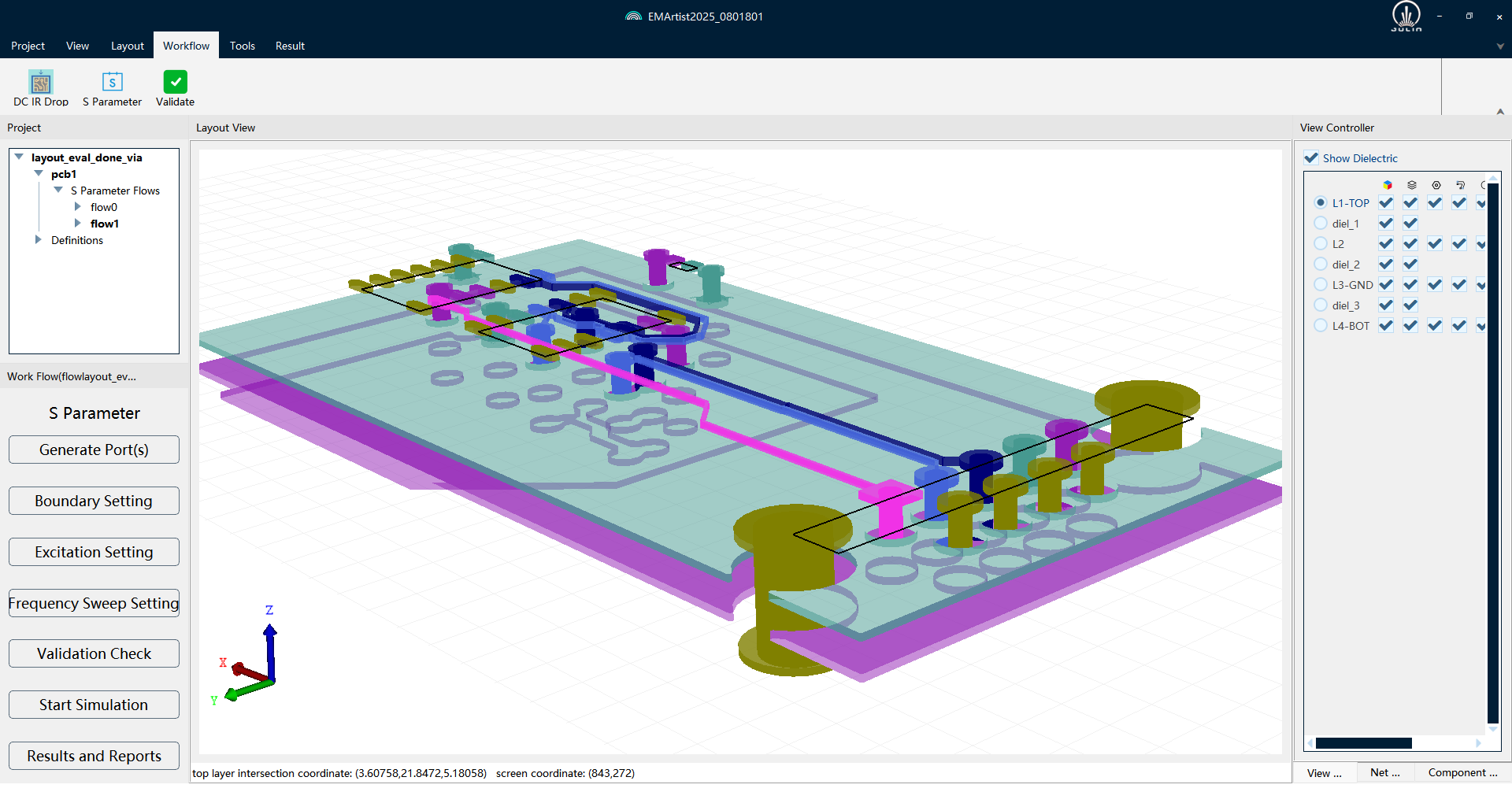

巨霖创始人孙家鑫:以Golden级精度SI/PI签核平台SIDesigner,赋能高保真系统设计2025.12.01

巨霖创始人孙家鑫:以Golden级精度SI/PI签核平台SIDesigner,赋能高保真系统设计2025.12.01 -

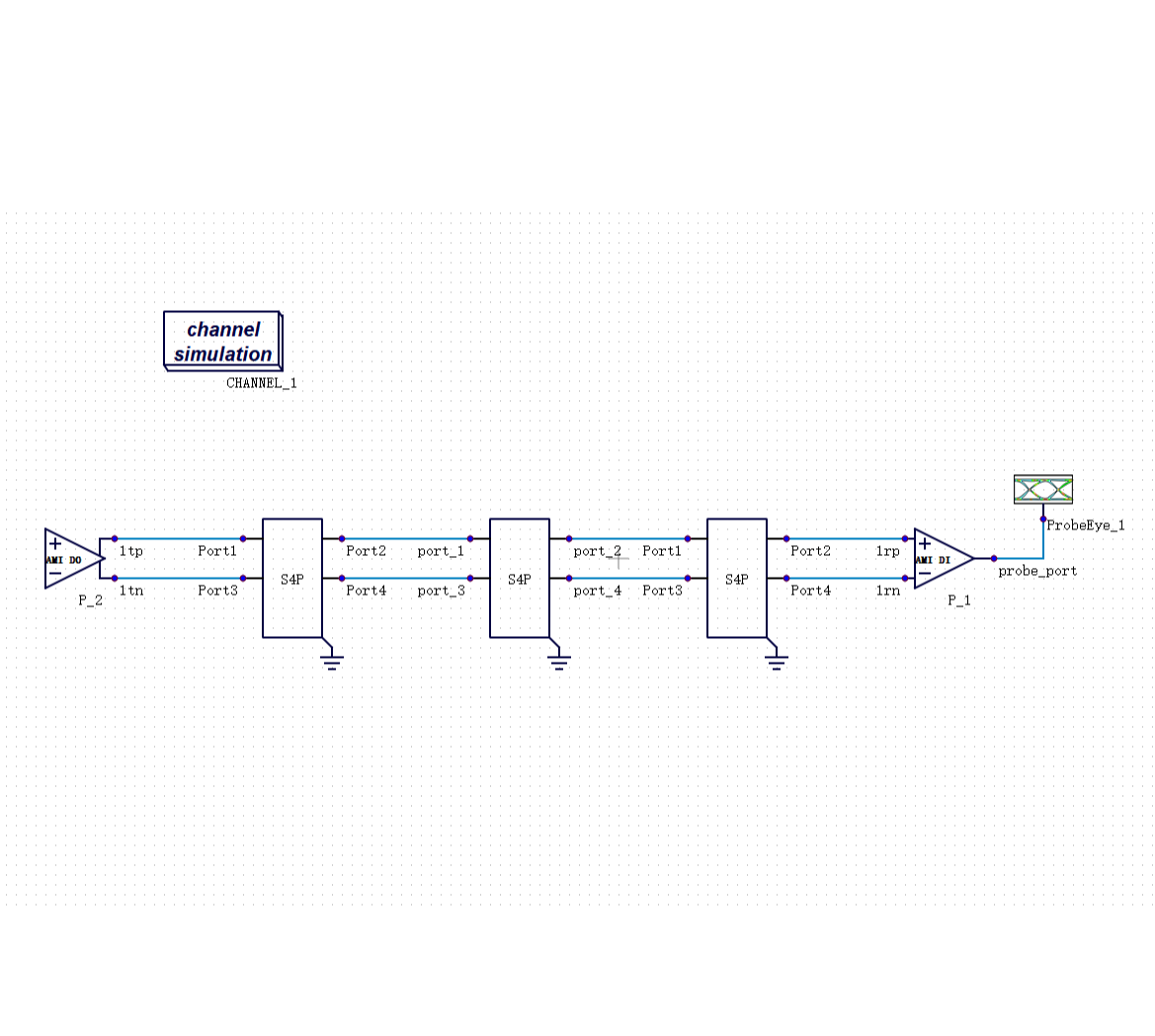

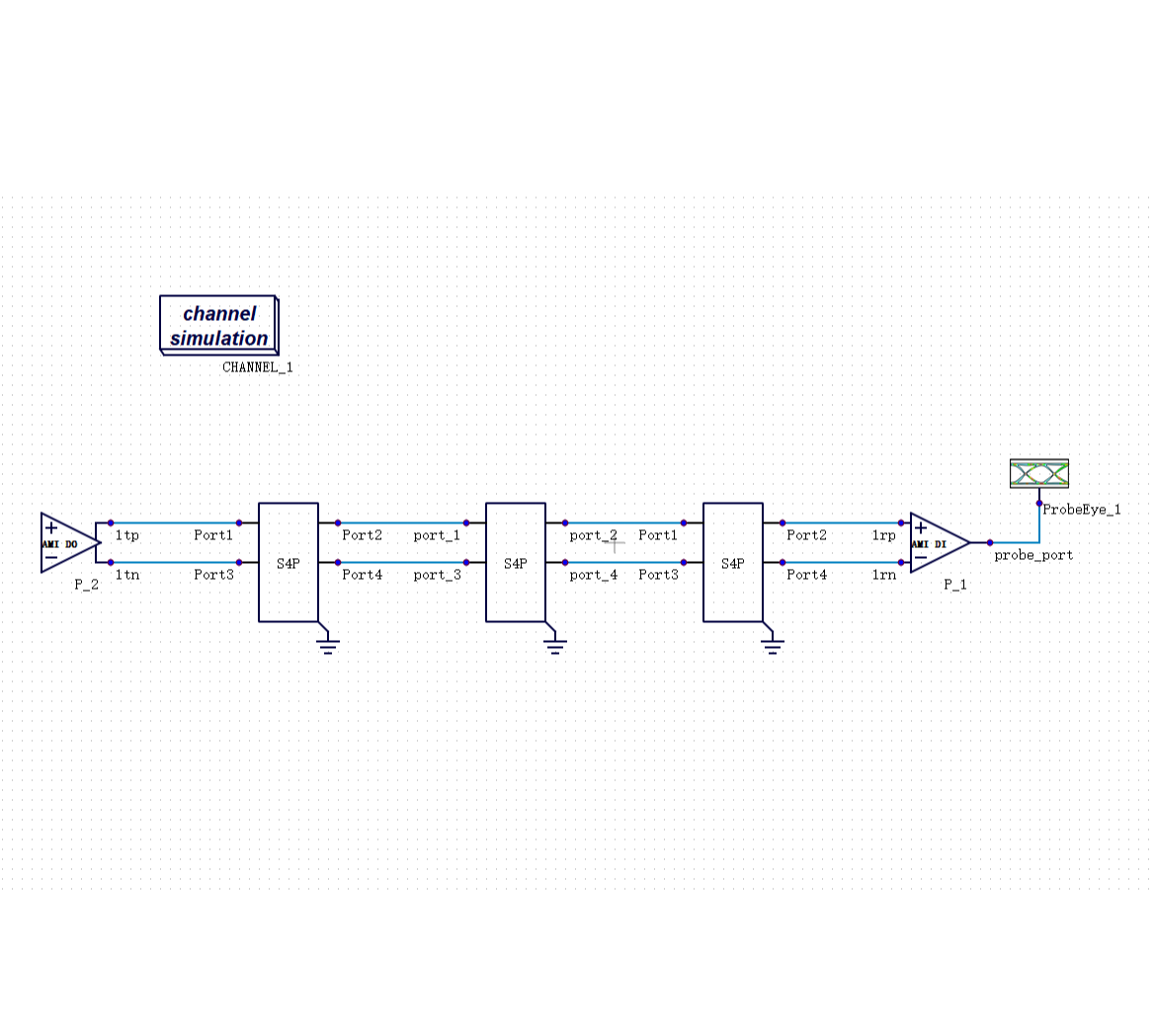

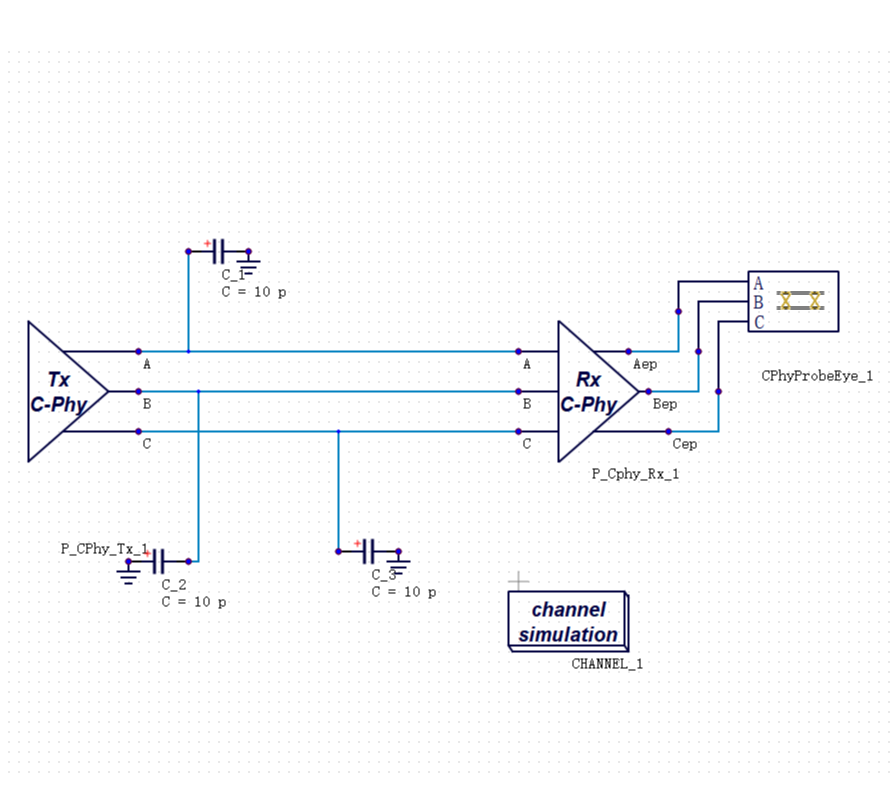

巨霖科技携一站式CPS SI/PI仿真平台亮相ICCAD2025.12.01

巨霖科技携一站式CPS SI/PI仿真平台亮相ICCAD2025.12.01 -

ICChina|攻克Chiplet仿真瓶颈 — 巨霖科技SIDesigner平台铸就高精度仿真“芯”基石2025.12.01

ICChina|攻克Chiplet仿真瓶颈 — 巨霖科技SIDesigner平台铸就高精度仿真“芯”基石2025.12.01 -

喜讯!巨霖科技荣获“湾芯奖-技术创新奖”2025.10.16

喜讯!巨霖科技荣获“湾芯奖-技术创新奖”2025.10.16