-

2026.03.20PanosSPICE:确立芯片级仿真的"黄金底座"查看更多

2026.03.20PanosSPICE:确立芯片级仿真的"黄金底座"查看更多 -

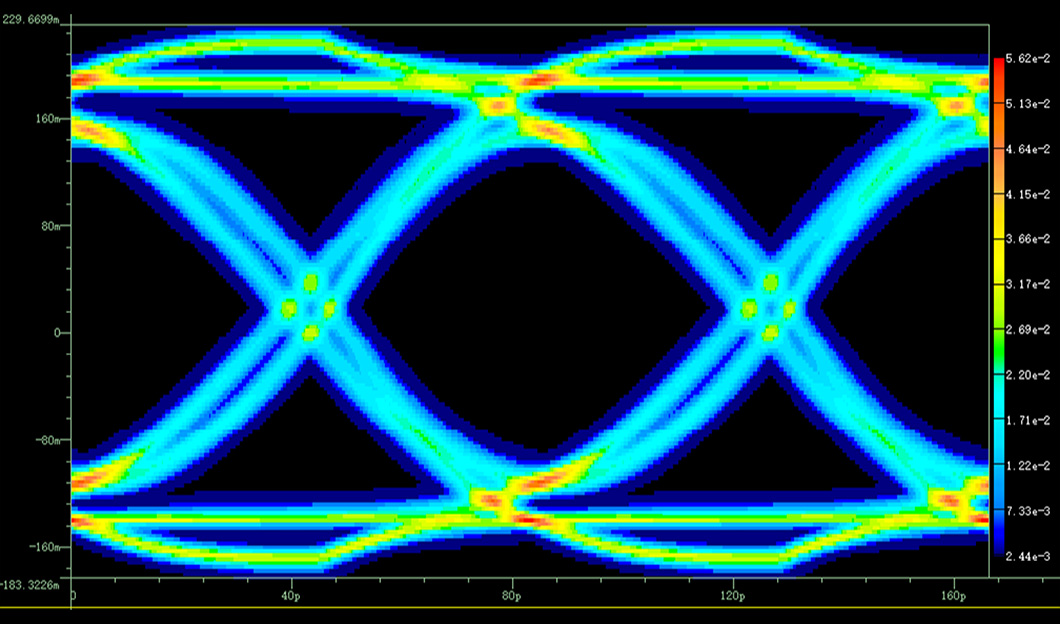

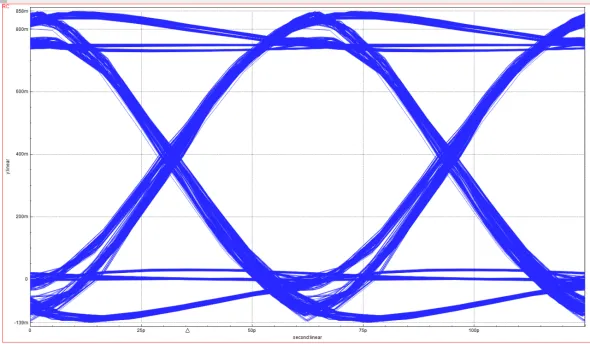

2026.03.13复杂芯片设计中的SPICE仿真困境:精度与效率的权衡之道

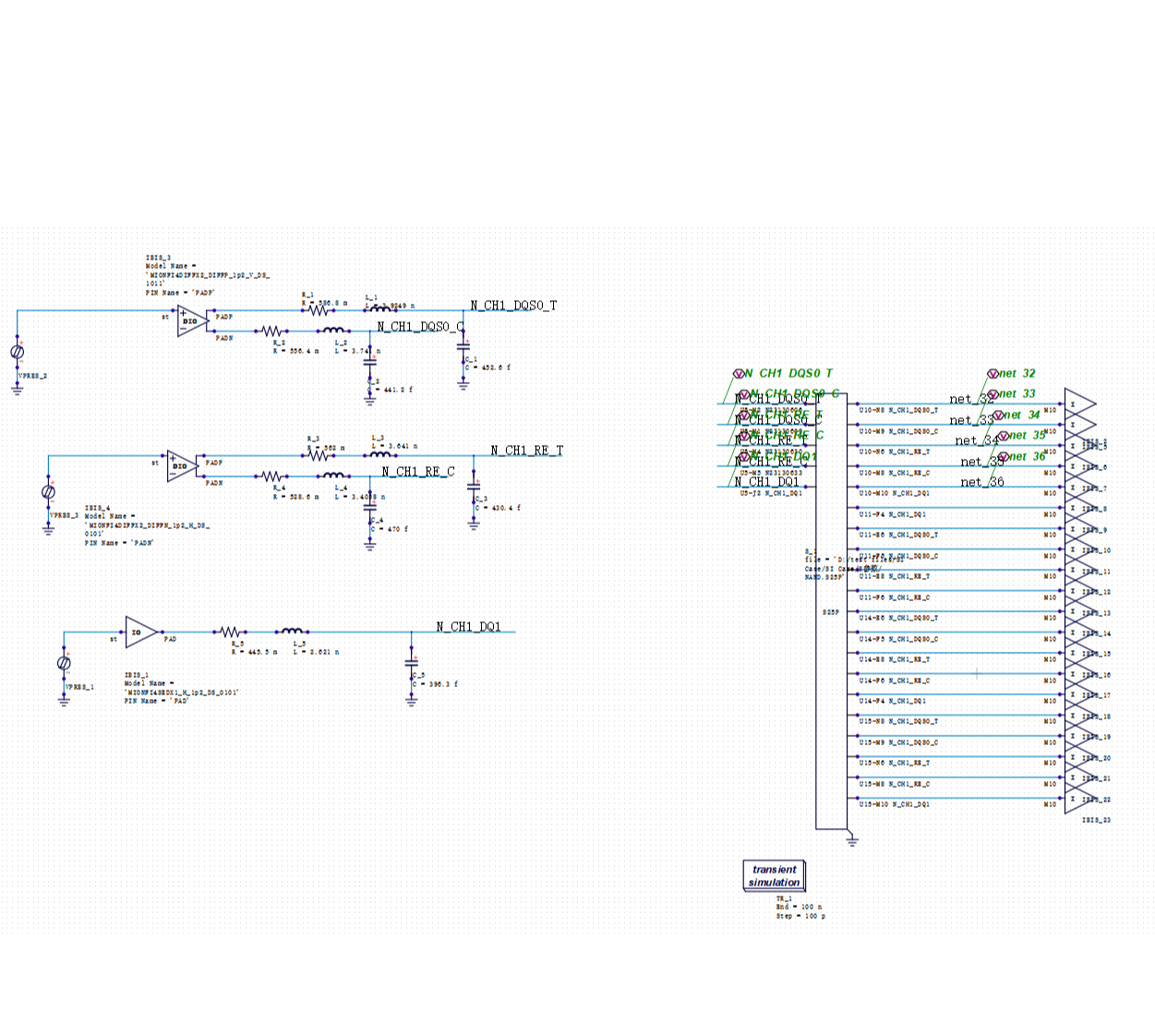

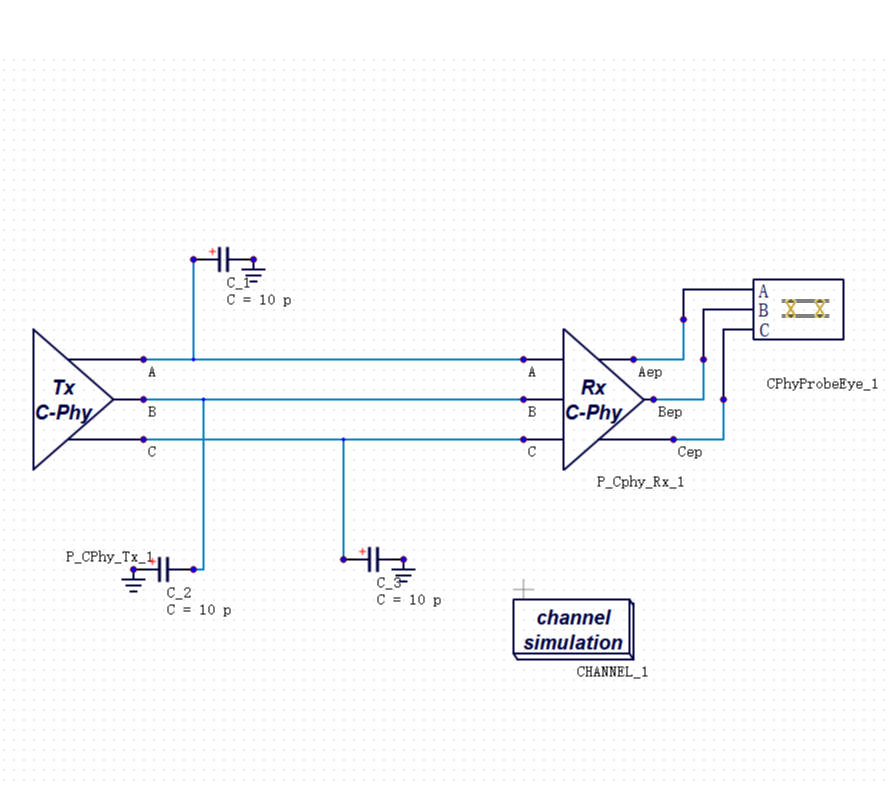

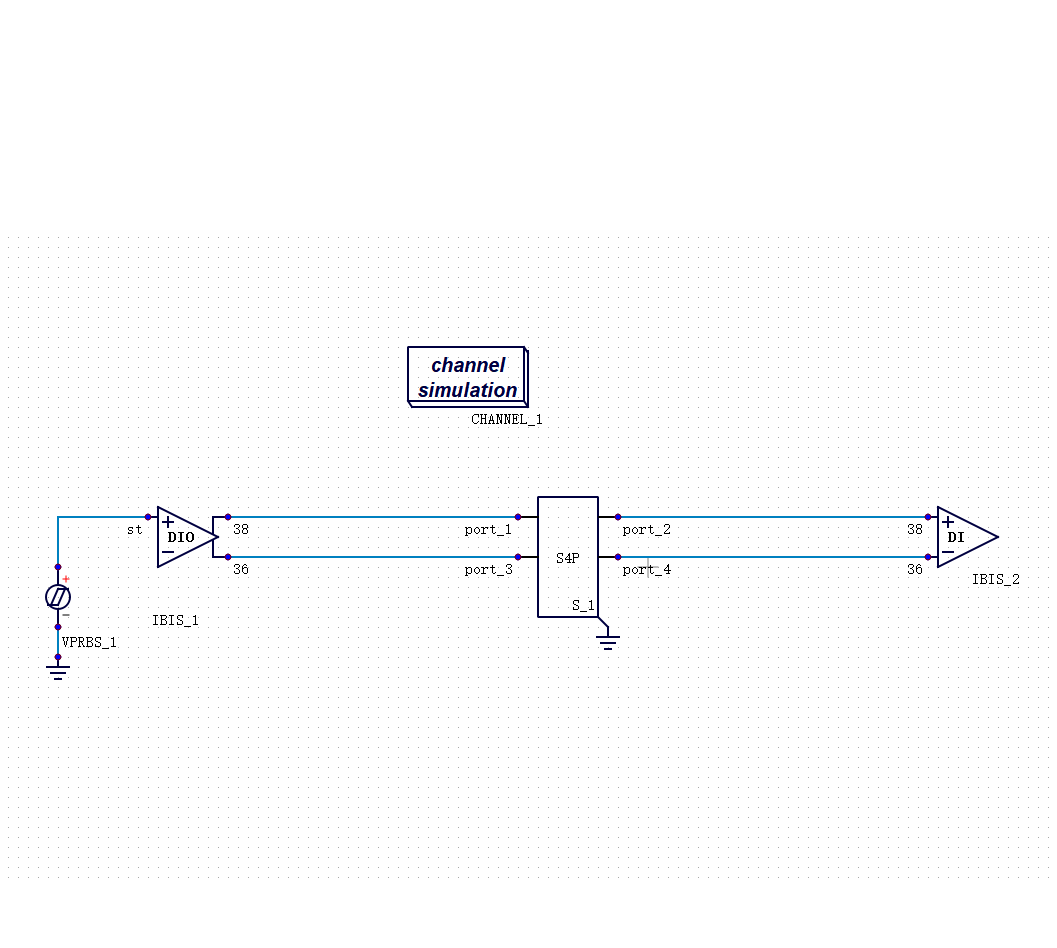

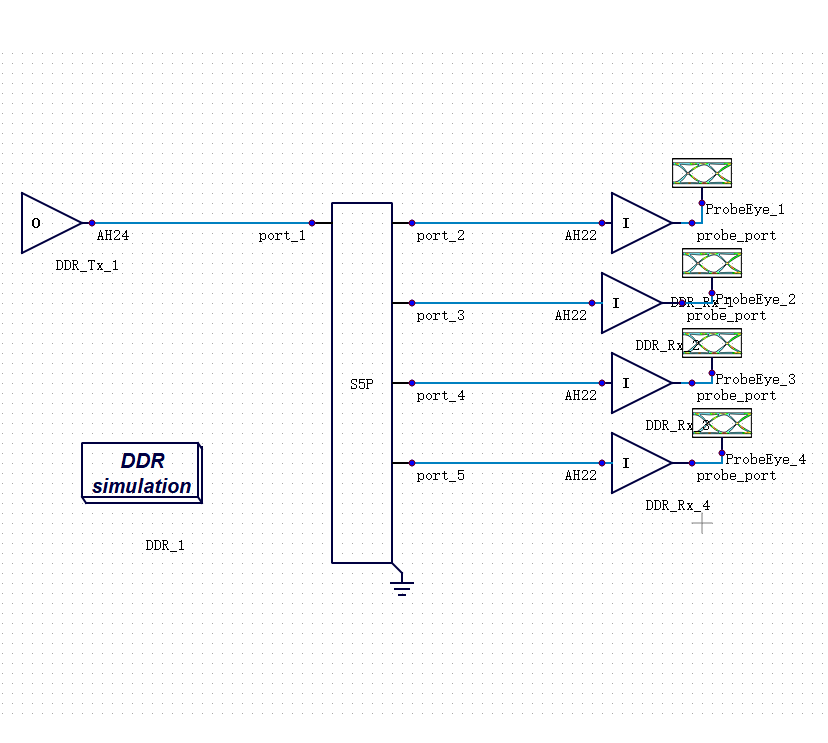

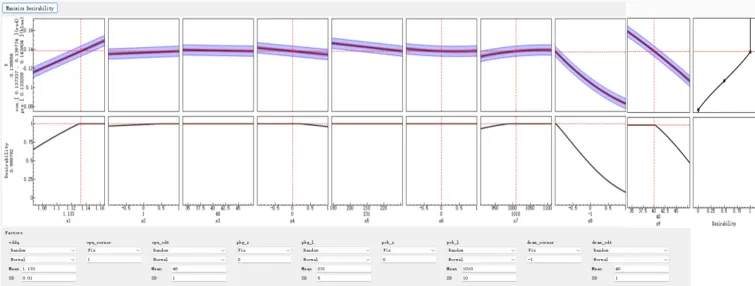

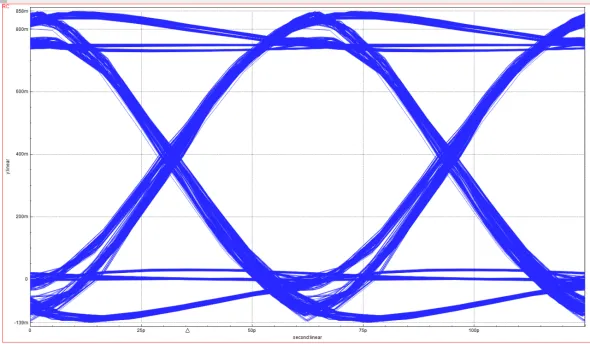

2026.03.13复杂芯片设计中的SPICE仿真困境:精度与效率的权衡之道核心观点概览 · 高速接口设计面临精度与效率的两难困境 · 传统 True-SPICE 精度高但耗时数周,FastSPICE快但精度有损 · 全晶体管级物理建模是解决根本问题的技术路径——唯有器件模型足够准,系统级验证才有可信基础

查看更多 -

2025.10.29Chiplet封装设计面临多维仿真挑战,信号与电源完整性成关键技术瓶颈查看更多

2025.10.29Chiplet封装设计面临多维仿真挑战,信号与电源完整性成关键技术瓶颈查看更多 -

2025.08.12UCIe协议: 推动Chiplet发展的关键力量查看更多

2025.08.12UCIe协议: 推动Chiplet发展的关键力量查看更多 -

2025.07.28电源噪声:电子系统的 “暗礁” 与应对策略

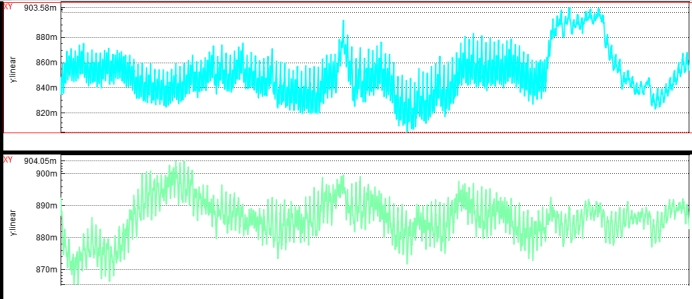

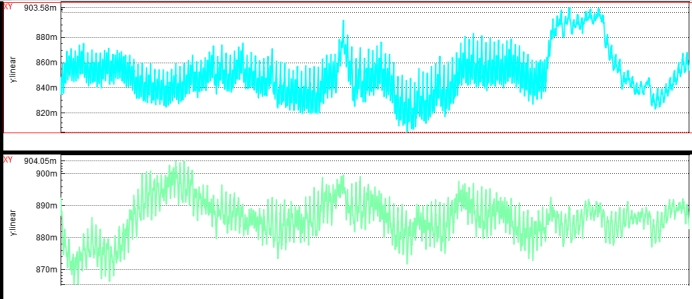

2025.07.28电源噪声:电子系统的 “暗礁” 与应对策略在电子系统的复杂海洋中,电源噪声如同隐匿的暗礁,悄无声息地威胁着系统的稳定运行。从精密的消费电子产品到庞大的工业控制系统,电源噪声的影响无处不在。本文将深入剖析电源噪声的本质、危害,并结合实际电路模型探讨应对策略,为电子系统的可靠设计筑牢根基。

查看更多 -

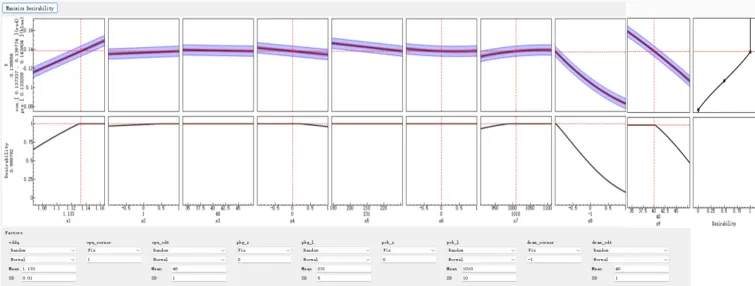

2025.07.08DFQ换新颜——全面提升用户体验查看更多

2025.07.08DFQ换新颜——全面提升用户体验查看更多 -

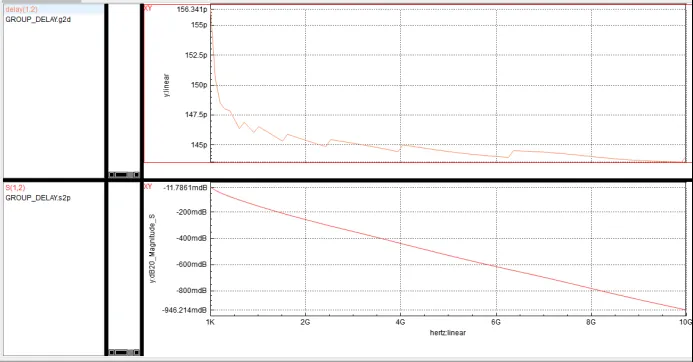

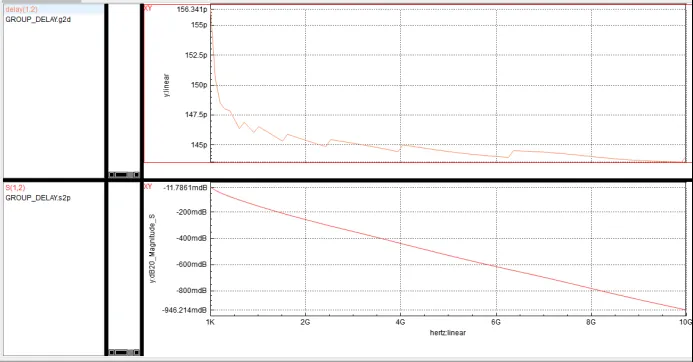

2025.07.03群延迟:信号传输中的隐形守护者

2025.07.03群延迟:信号传输中的隐形守护者在高速数字通信和射频系统中,信号从发送端到接收端的传输过程中会遇到各种失真和畸变。群延迟(Group Delay)作为描述系统相位线性度的重要参数,直接影响着信号保真度和系统性能。本文将深入浅出地介绍群延迟的基本概念、应用场景,并通过仿真示例展示其在实际工程中的重要性。

查看更多 -

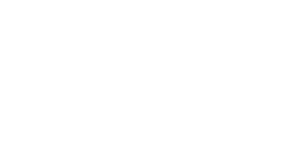

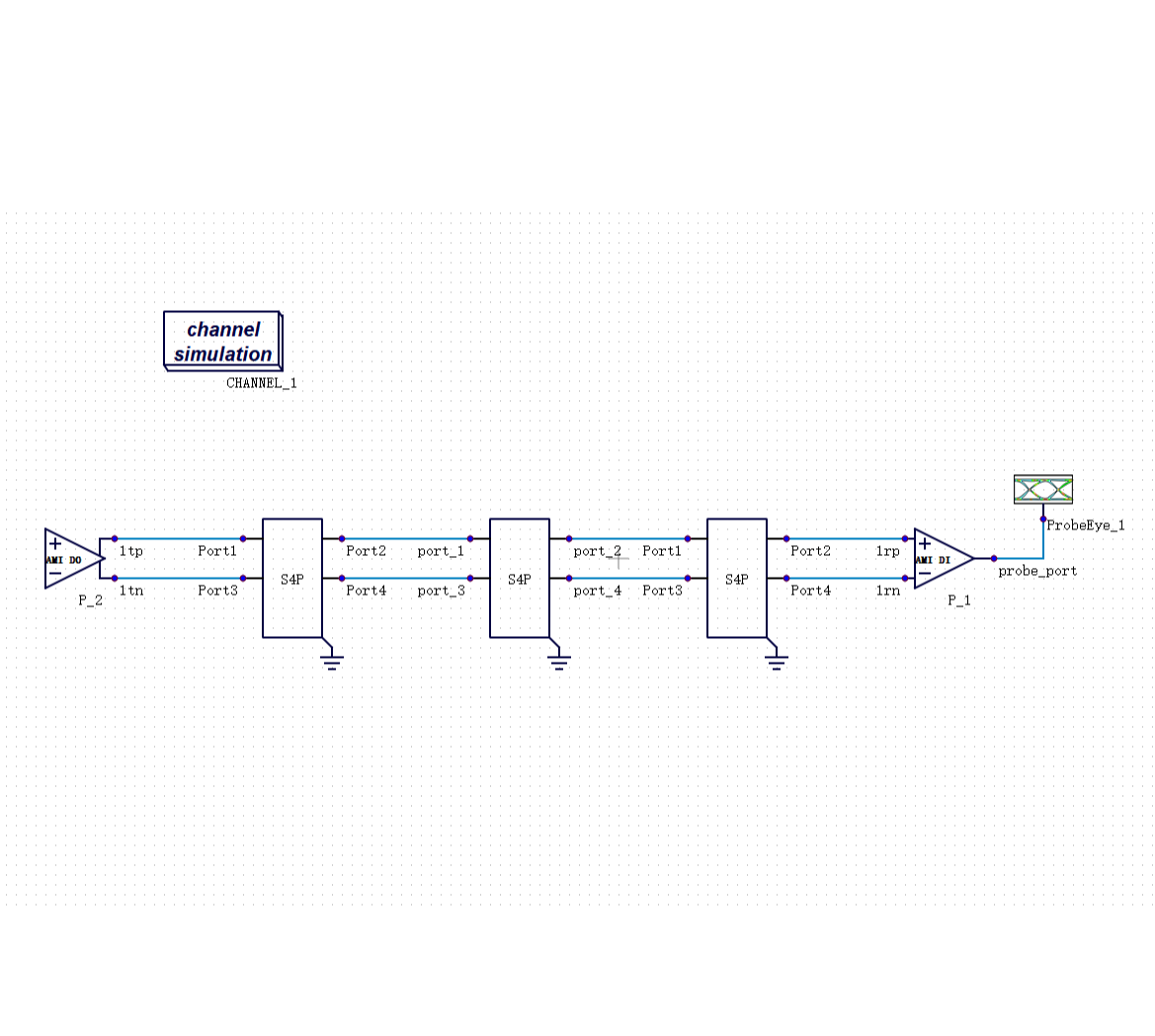

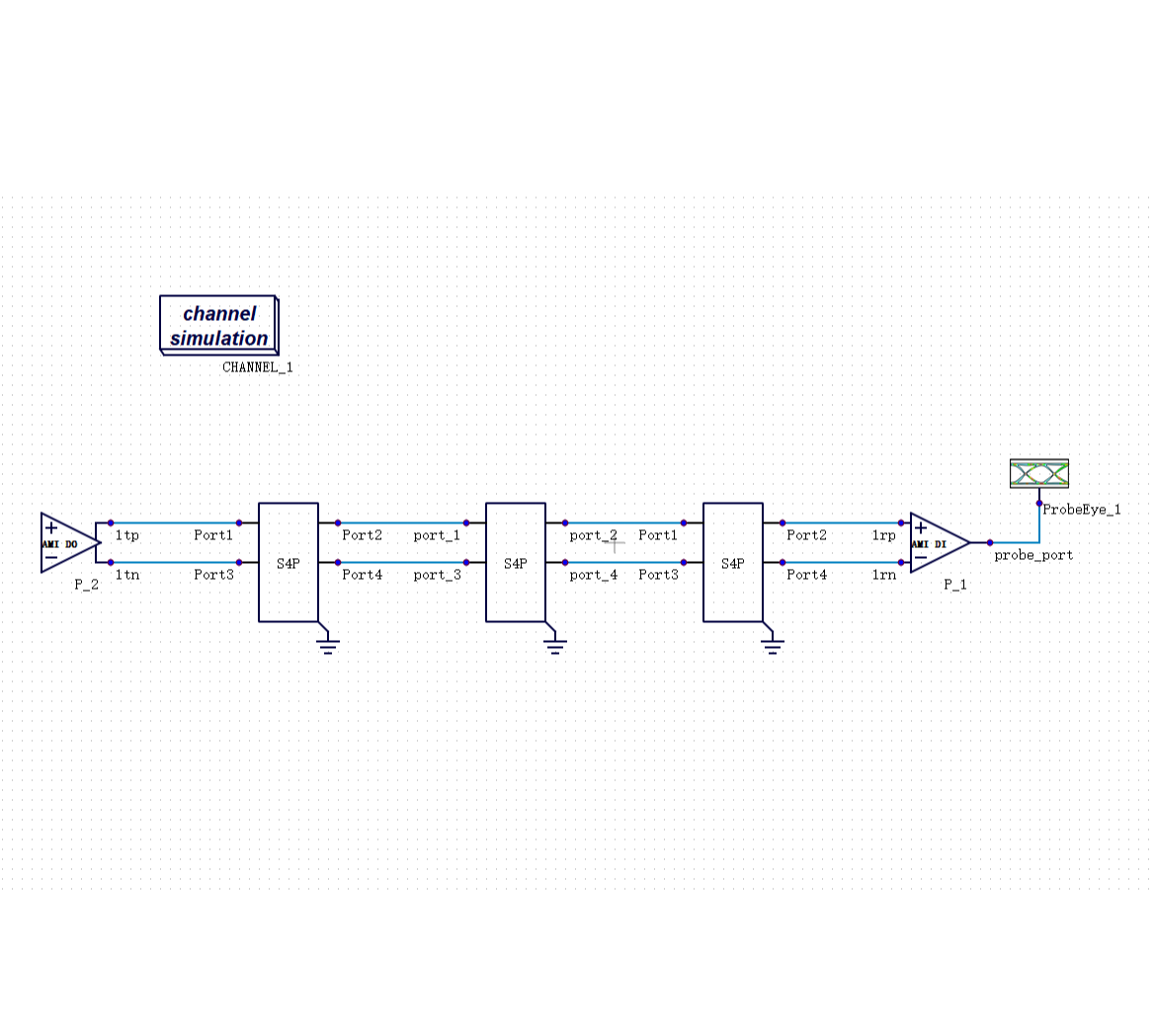

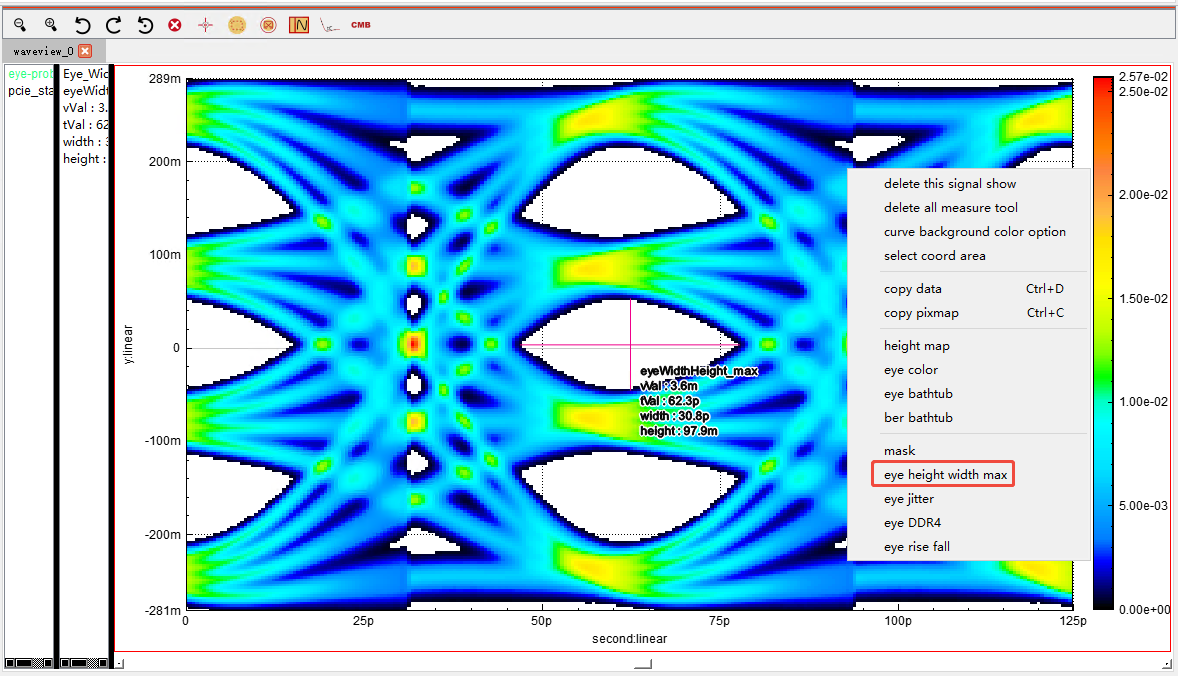

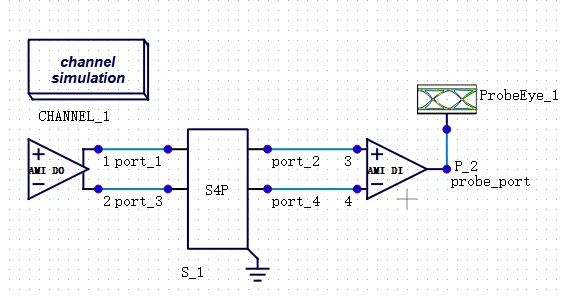

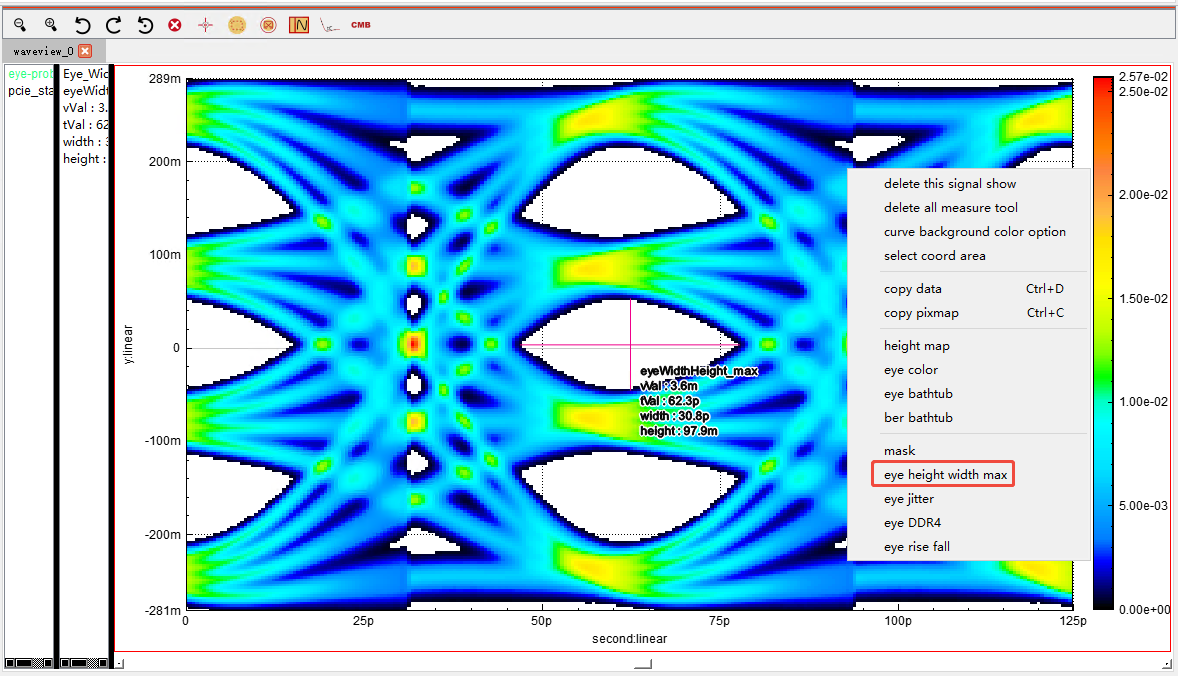

2025.06.09使用SIDesigner轻松仿真PCIe场景查看更多

2025.06.09使用SIDesigner轻松仿真PCIe场景查看更多 -

2025.06.04XSR 技术:芯片间互连的革新力量查看更多

2025.06.04XSR 技术:芯片间互连的革新力量查看更多 -

2025.05.13DFQ让设计更加优秀查看更多

2025.05.13DFQ让设计更加优秀查看更多

探索更多

-

高速接口的速率翻了十倍,SI/PI仿真的难度何止翻了十倍2026.04.14

高速接口的速率翻了十倍,SI/PI仿真的难度何止翻了十倍2026.04.14 -

PanosSPICE:确立芯片级仿真的"黄金底座"2026.03.20

PanosSPICE:确立芯片级仿真的"黄金底座"2026.03.20 -

复杂芯片设计中的SPICE仿真困境:精度与效率的权衡之道2026.03.13

复杂芯片设计中的SPICE仿真困境:精度与效率的权衡之道2026.03.13 -

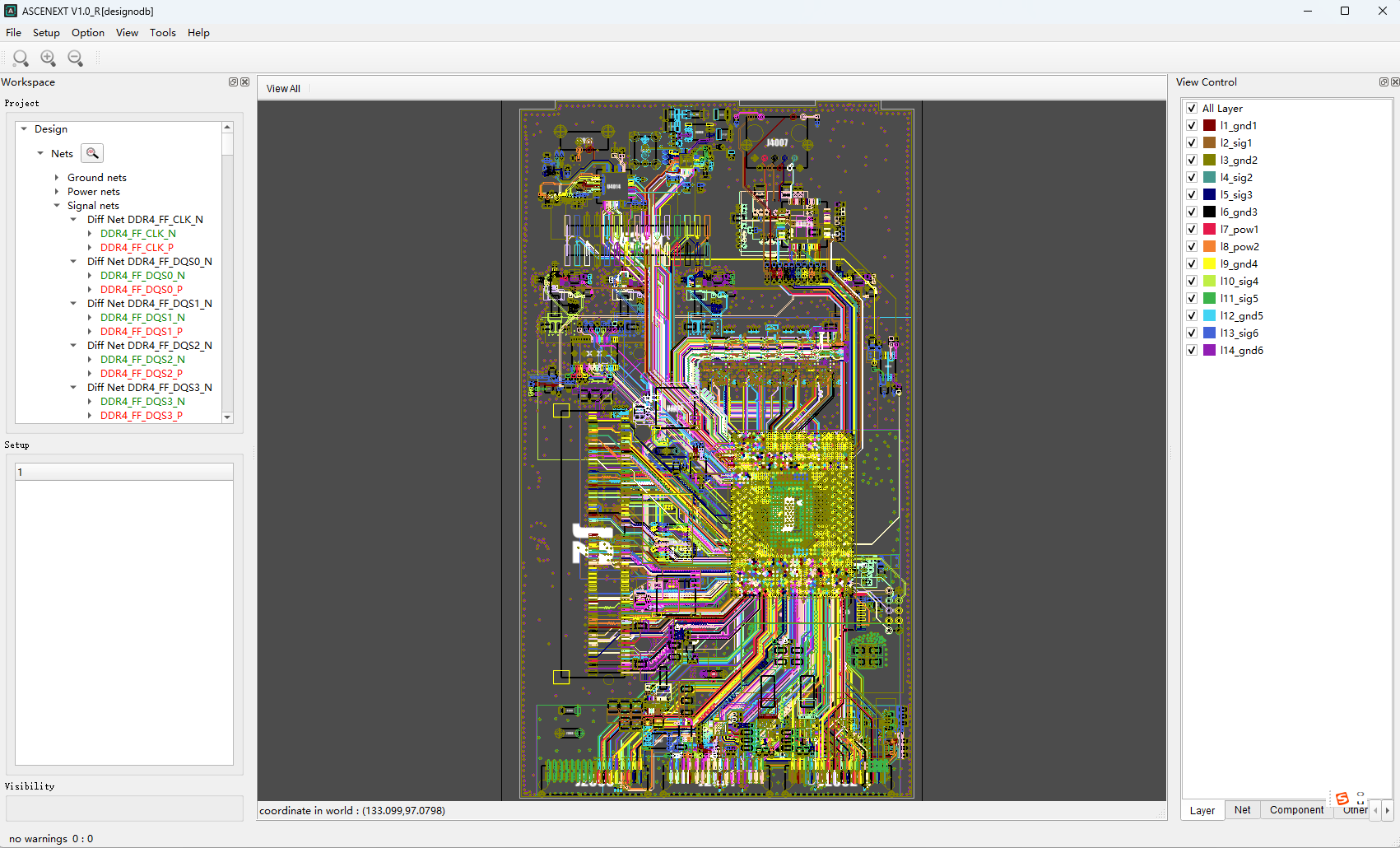

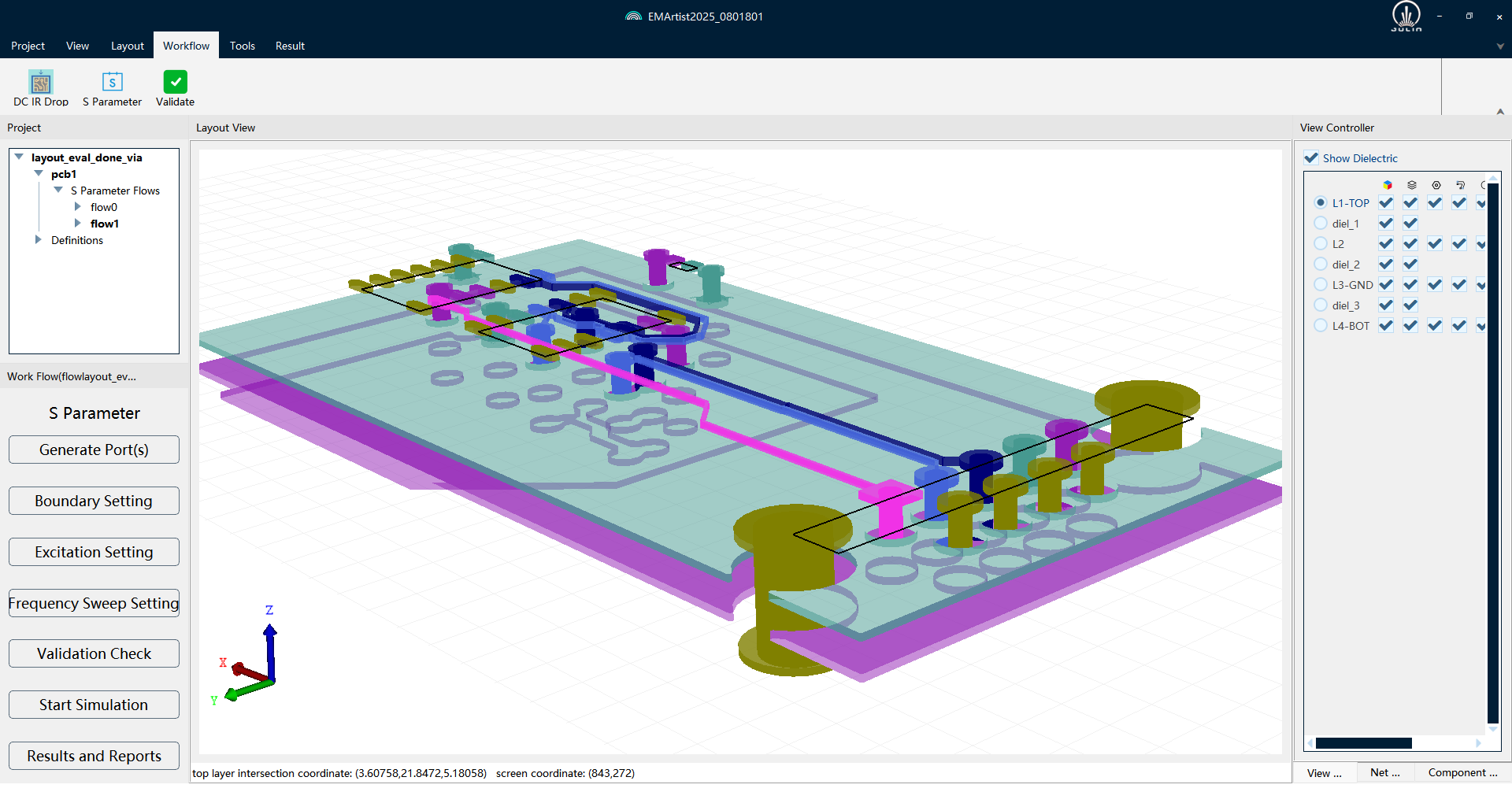

Chiplet封装设计面临多维仿真挑战,信号与电源完整性成关键技术瓶颈2025.10.29

Chiplet封装设计面临多维仿真挑战,信号与电源完整性成关键技术瓶颈2025.10.29 -

UCIe协议: 推动Chiplet发展的关键力量2025.08.12

UCIe协议: 推动Chiplet发展的关键力量2025.08.12 -

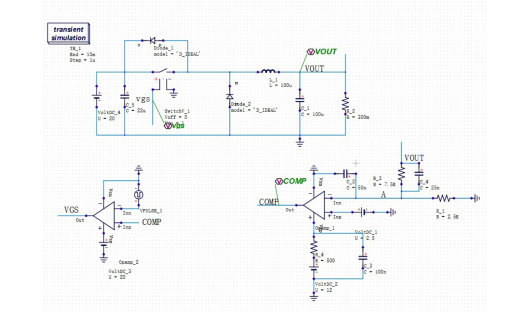

电源噪声:电子系统的 “暗礁” 与应对策略2025.07.28

电源噪声:电子系统的 “暗礁” 与应对策略2025.07.28 -

DFQ换新颜——全面提升用户体验2025.07.08

DFQ换新颜——全面提升用户体验2025.07.08 -

群延迟:信号传输中的隐形守护者2025.07.03

群延迟:信号传输中的隐形守护者2025.07.03 -

使用SIDesigner轻松仿真PCIe场景2025.06.09

使用SIDesigner轻松仿真PCIe场景2025.06.09