-

2026.04.29Selecting SI Simulation Tools: Practical Verification of SIDesigner's 4 Core CapabilitiesRead More

2026.04.29Selecting SI Simulation Tools: Practical Verification of SIDesigner's 4 Core CapabilitiesRead More -

2026.04.23How to Choose DDR5/HBM3 Signal Integrity Simulation Tools? Four Verification StandardsRead More

2026.04.23How to Choose DDR5/HBM3 Signal Integrity Simulation Tools? Four Verification StandardsRead More -

2026.03.20PanosSPICE: Establishing the "Golden Foundation" for Chip-Level SimulationRead More

2026.03.20PanosSPICE: Establishing the "Golden Foundation" for Chip-Level SimulationRead More -

2026.03.13The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and EfficiencyRead More

2026.03.13The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and EfficiencyRead More -

2025.10.29Beyond Moore’s Law: Navigating SI/PI and Multi-physics Challenges in Chiplet Heterogeneous IntegrationRead More

2025.10.29Beyond Moore’s Law: Navigating SI/PI and Multi-physics Challenges in Chiplet Heterogeneous IntegrationRead More -

2025.07.28Power Noise: Navigating the "Hidden Reefs" of Electronic Systems and Mitigation Strategies

2025.07.28Power Noise: Navigating the "Hidden Reefs" of Electronic Systems and Mitigation StrategiesPower Noise: Navigating the "Hidden Reefs" of Electronic Systems and Mitigation Strategies

Read More -

2025.07.08DFQ Gets a New Look - Comprehensively Enhancing User ExperienceRead More

2025.07.08DFQ Gets a New Look - Comprehensively Enhancing User ExperienceRead More -

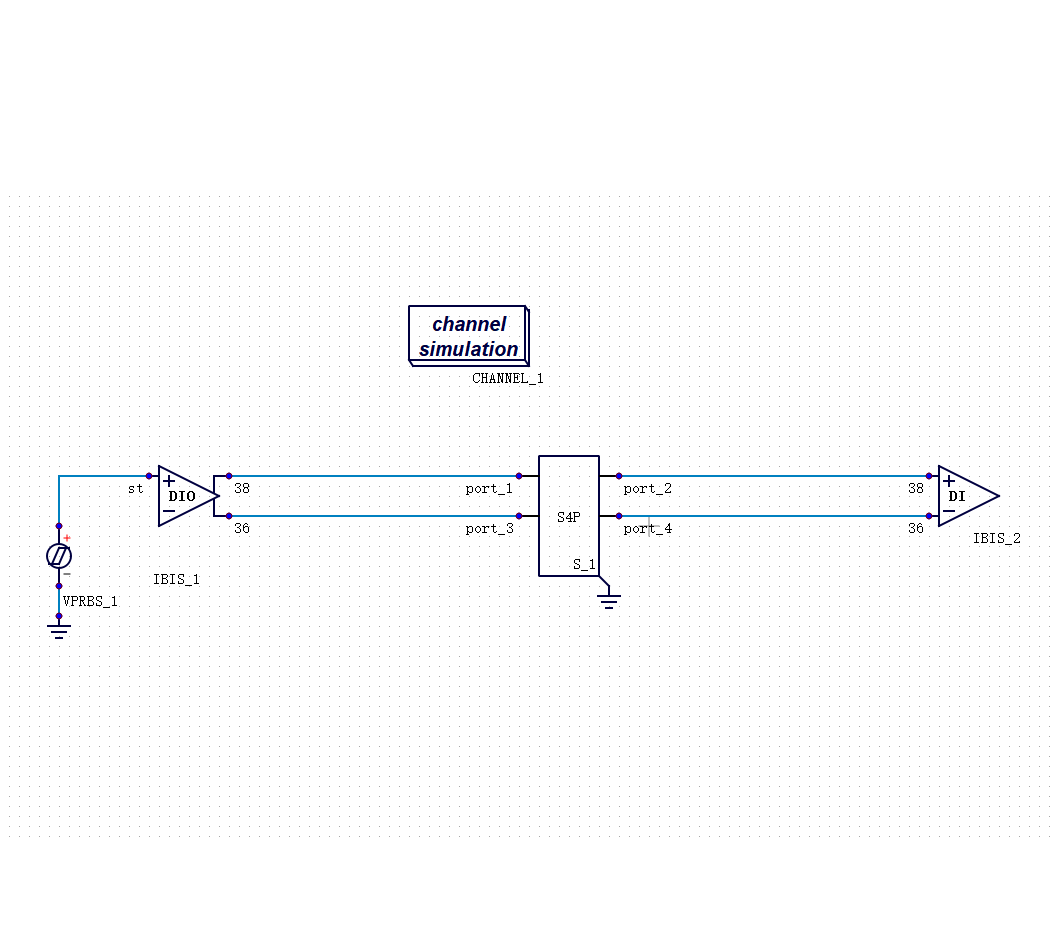

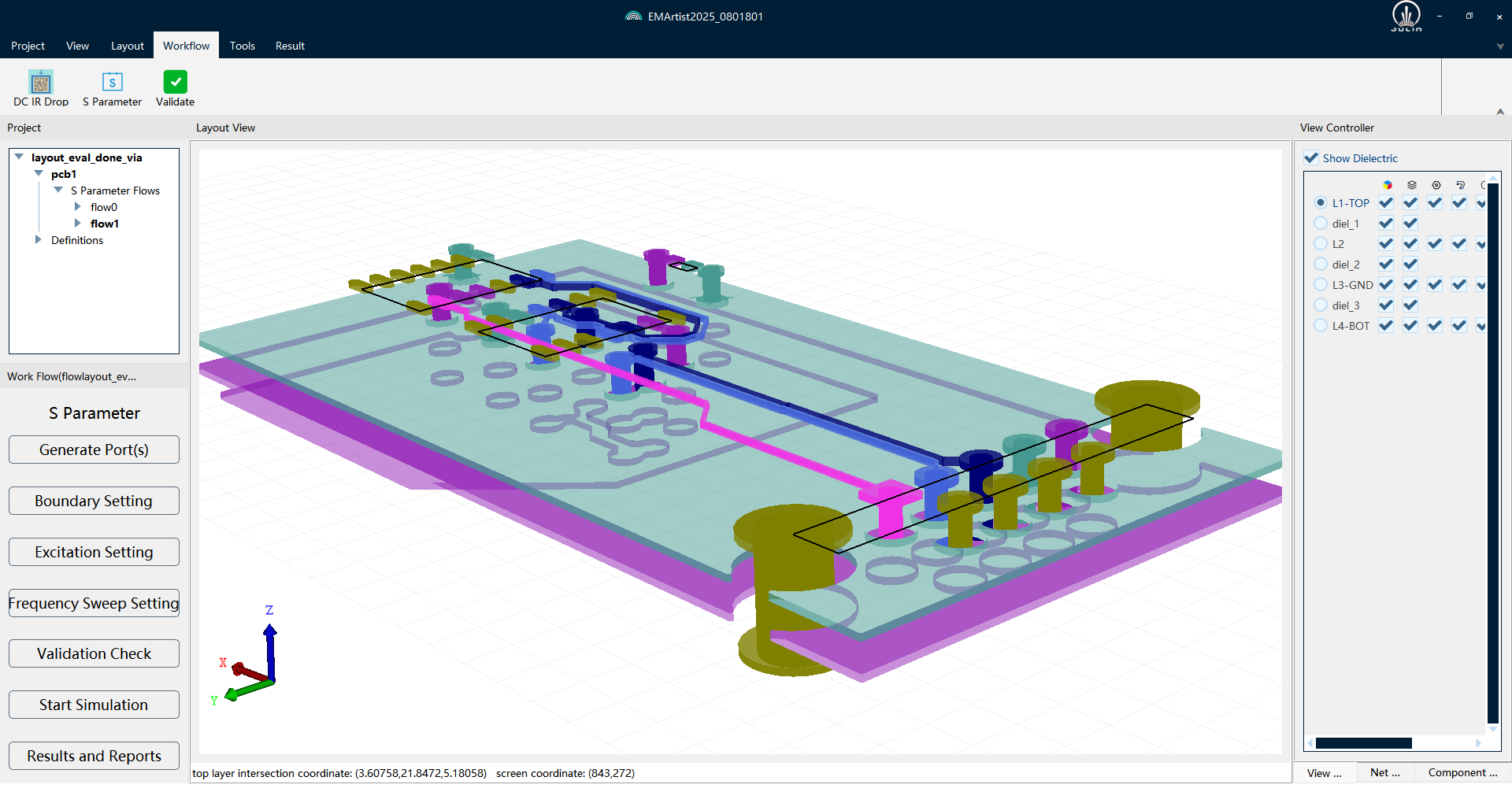

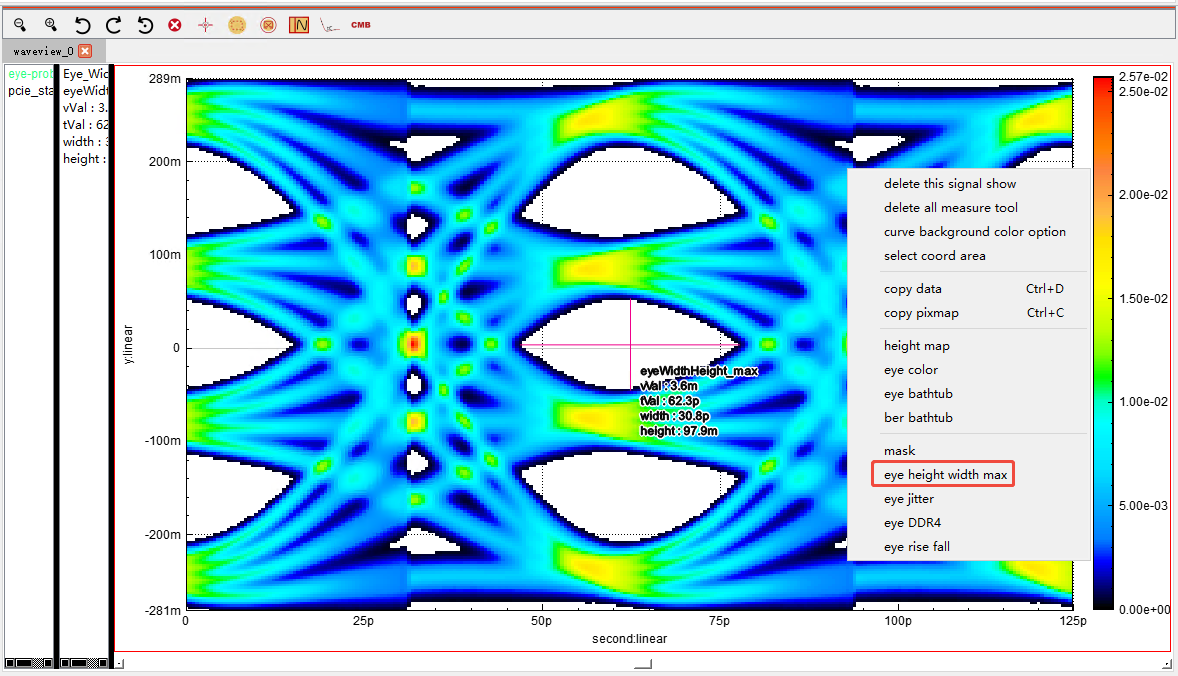

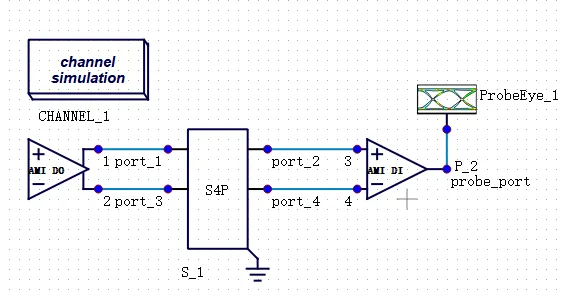

2025.06.09Easy Simulation of PCIe Scenarios with SIDesignerRead More

2025.06.09Easy Simulation of PCIe Scenarios with SIDesignerRead More -

2025.06.04XSR Technology: The Innovative Force Driving Inter-Chip InterconnectsRead More

2025.06.04XSR Technology: The Innovative Force Driving Inter-Chip InterconnectsRead More

Read More

-

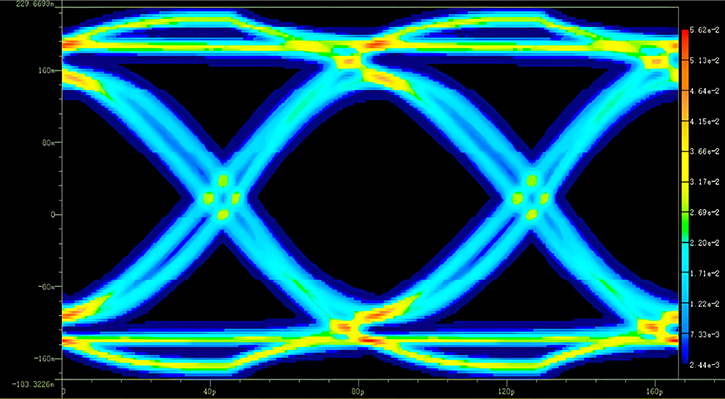

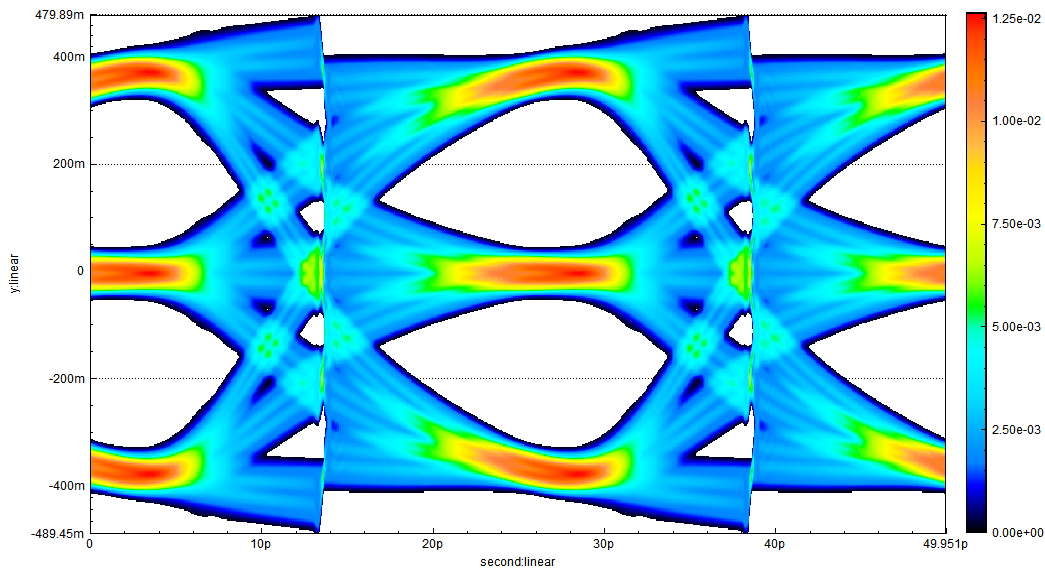

PAM3 Encoding and Simulating Verification in High-Speed Transmission2025.03.31

PAM3 Encoding and Simulating Verification in High-Speed Transmission2025.03.31 -

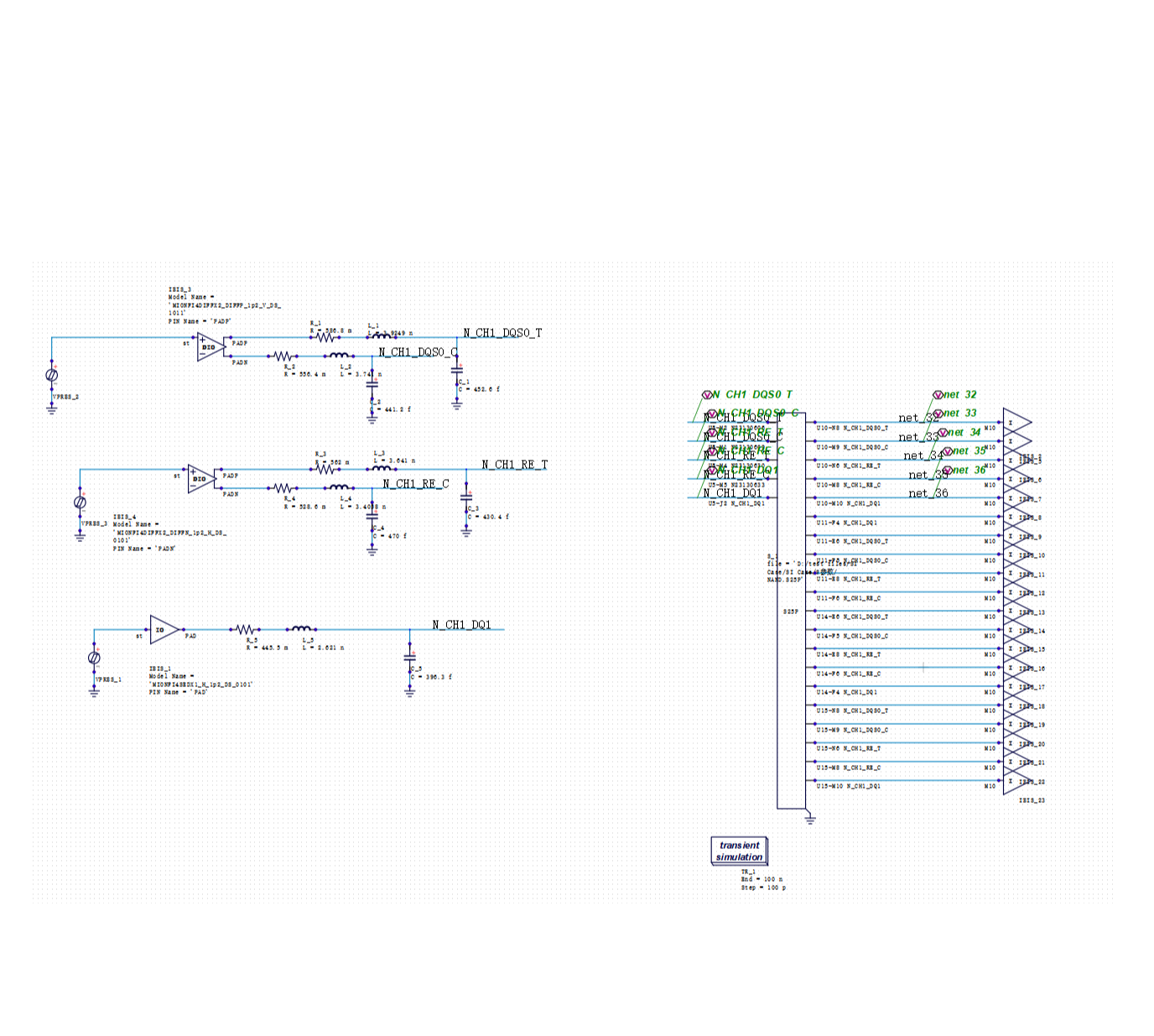

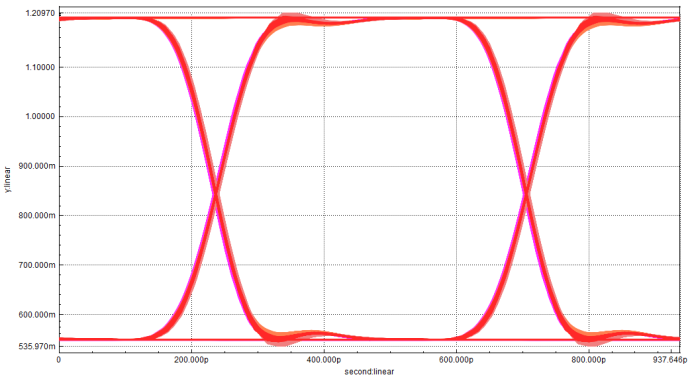

HBM Introduction and Simulation2025.03.26

HBM Introduction and Simulation2025.03.26 -

PCIe 6.0 Introduction and Simulation2025.03.20

PCIe 6.0 Introduction and Simulation2025.03.20 -

Introduction to NAND Flash Memory2025.03.12

Introduction to NAND Flash Memory2025.03.12 -

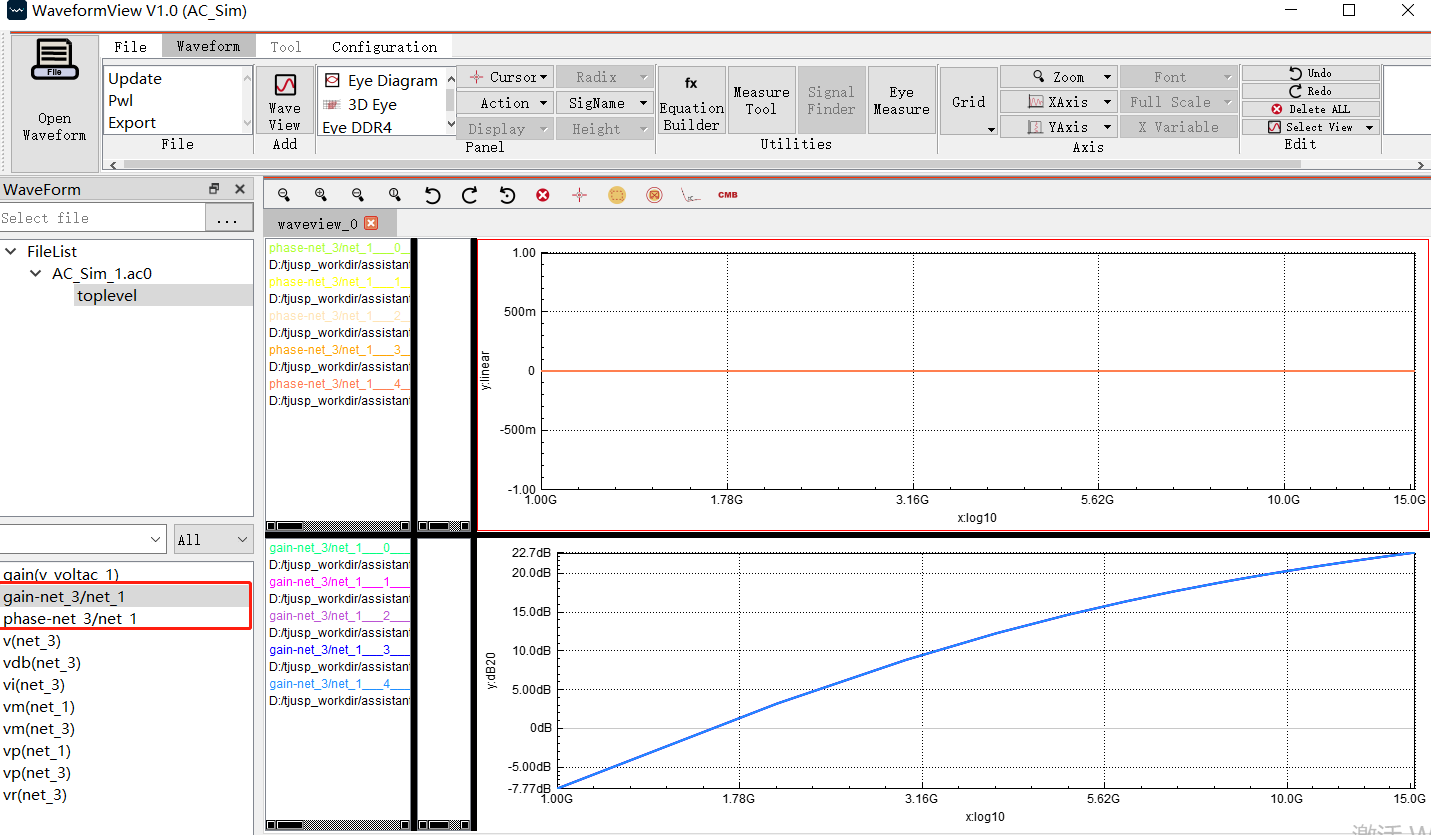

Introduction to Loop Simulation2025.03.04

Introduction to Loop Simulation2025.03.04 -

Power-Aware IBIS Model Introduction and Application2025.02.27

Power-Aware IBIS Model Introduction and Application2025.02.27 -

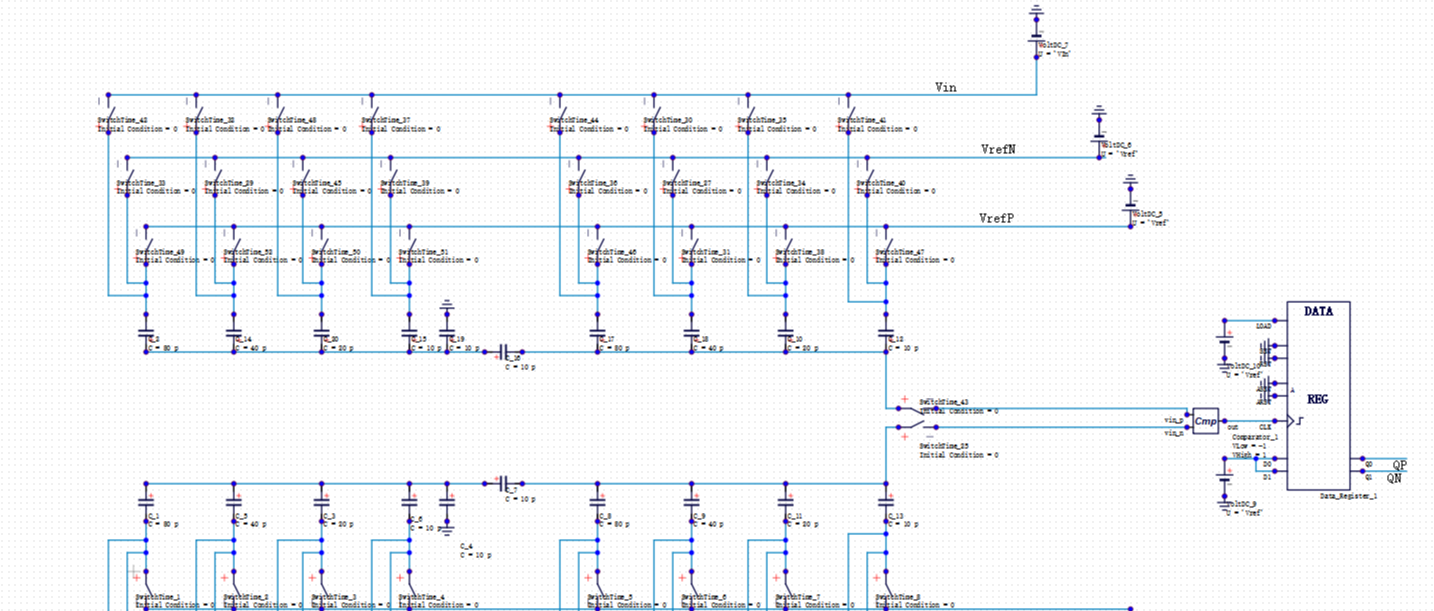

All Digital Calibration in SARADC2025.02.21

All Digital Calibration in SARADC2025.02.21 -

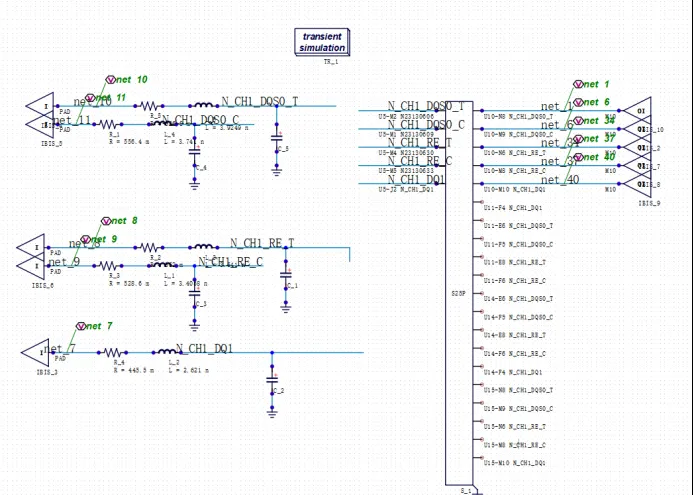

SIDesigner is dedicated to comprehensively addressing the signal integrity challenges faced by DDR2025.02.11

SIDesigner is dedicated to comprehensively addressing the signal integrity challenges faced by DDR2025.02.11 -

Analysis and Simulation of Phase Noise of LC Oscillator2025.01.17

Analysis and Simulation of Phase Noise of LC Oscillator2025.01.17